|

|

PDF ADC12762CCV Data sheet ( Hoja de datos )

| Número de pieza | ADC12762CCV | |

| Descripción | 12-Bit/ 1.4 MHz/ 300 mW A/D Converter with Input Multiplexer and Sample/Hold | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de ADC12762CCV (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

June 1999

ADC12762

12-Bit, 1.4 MHz, 300 mW A/D Converter

with Input Multiplexer and Sample/Hold

General Description

Using an innovative multistep conversion technique, the

12-bit ADC12762 CMOS analog-to-digital converter digitizes

signals at a 1.4 MHz sampling rate while consuming a maxi-

mum of only 300 mW on a single +5V supply. The

ADC12762 performs a 12-bit conversion in three

lower-resolution “flash” conversions, yielding a fast A/D with-

out the cost and power dissipation associated with true flash

approaches.

The analog input voltage to the ADC12762 is tracked and

held by an internal sampling circuit, allowing high frequency

input signals to be accurately digitized without the need for

an external sample-and-hold circuit. The ADC12762 features

two sample-and-hold/flash comparator sections which allow

the converter to acquire one sample while converting the

previous. This pipelining technique increases conversion

speed without sacrificing performance. The multiplexer out-

put is available to the user in order to perform additional ex-

ternal signal processing before the signal is digitized.

When the converter is not digitizing signals, it can be placed

in the Standby mode; typical power consumption in this

mode is 250 µW.

Features

n Built-in sample-and-hold

n Single +5V supply

n Single channel or 2 channel multiplexer operation

Key Specifications

n Sampling rate

n Conversion time

n SNR, fIN= 100 kHz

n Power dissipation (fs= 1.4 MHz)

n No missing codes over temperature

1.4 MHz (min)

593 ns (typ)

67.5 dB (min)

300 mW (max)

Guaranteed

Applications

n CCD image scanners

n Digital signal processor front ends

n Instrumentation

n Disk drives

n Mobile telecommunications

n Waveform digitizers

ADC12762 Block Diagram

Ordering Information

Commercial (0˚C ≤ TA ≤ +70˚C)

ADC12762CCV

ADC12062EVAL

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

© 1999 National Semiconductor Corporation DS012811

DS012811-1

Package

V44 Plastic Leaded Chip Carrier

Evaluation Board

www.national.com

1 page

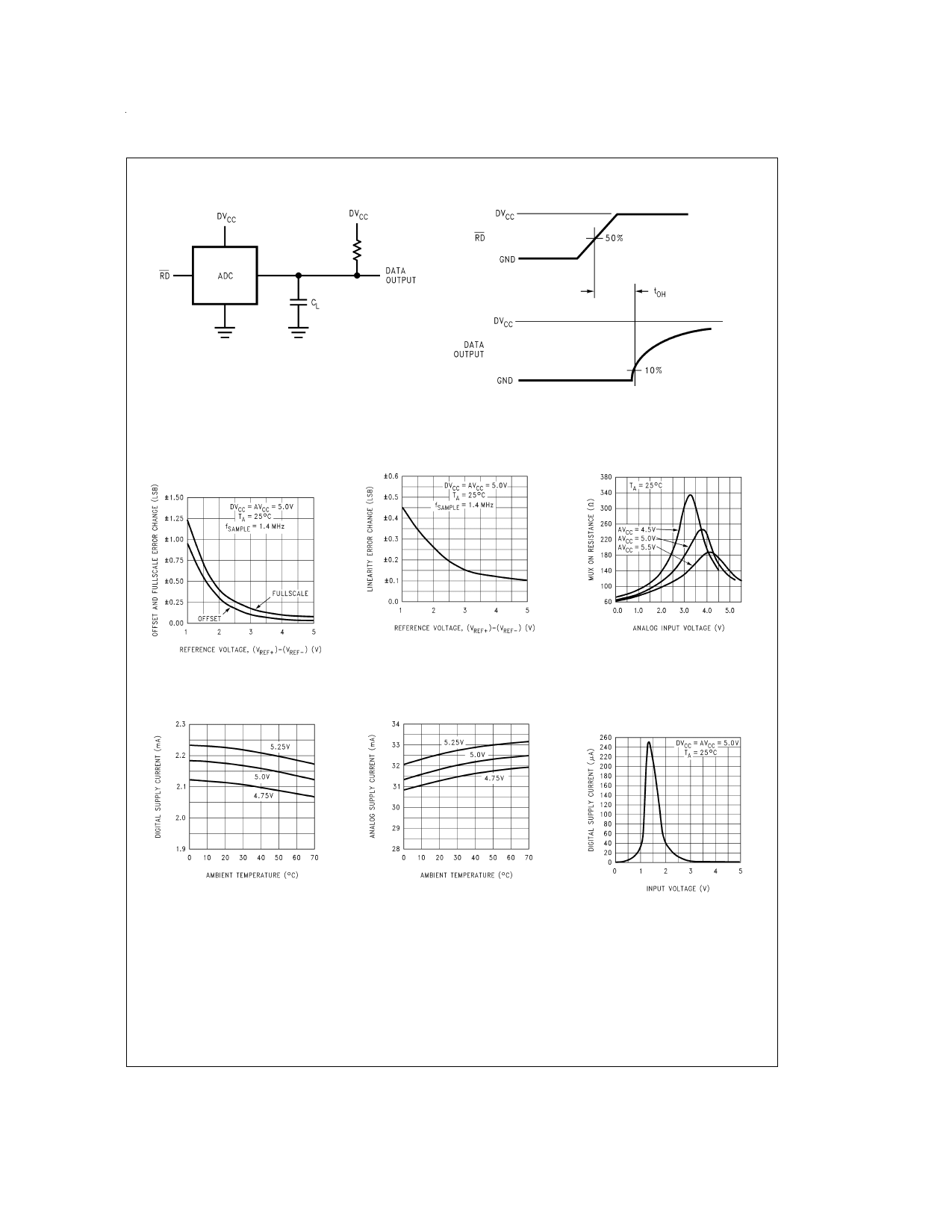

TRI-STATE Test Circuit and Waveforms (Continued)

DS012811-4

Typical Performance Characteristics

Offset and Fullscale

Error Change vs

Reference Voltage

Linearity Error Change

vs Reference Voltage

DS012811-5

Mux ON Resistance

vs Input Voltage

DS012811-6

Digital Supply Current

vs Temperature

DS012811-7

Analog Supply Current

vs Temperature

DS012811-8

Current Consumption in

Standby Mode vs Voltage

on Digital Input Pins

DS012811-9

DS012811-10

DS012811-11

5 www.national.com

5 Page

Functional Description (Continued)

The resistor string near the center of the block diagram in

Figure 4 generates the 6-bit and 10-bit reference voltages for

the first two conversions. Each of the 16 resistors at the bot-

tom of the string is equal to 1/1024 of the total string resis-

tance. These resistors form the LSB Ladder (The weight of

each resistor on the LSB ladder is actually equivalent to four

12-bit LSBs. It is called the LSB ladder because it has the

highest resolution of all the ladders in the converter) and

have a voltage drop of 1/1024 of the total reference voltage

(VREF+ − VREF−) across each of them. The remaining resis-

tors form the MSB Ladder. It is comprised of eight groups of

eight resistors each connected in series (the lowest MSB

ladder resistor is actually the entire LSB ladder). Each MSB

Ladder section has 1⁄8 of the total reference voltage across it.

Within a given MSB ladder section, each of the eight MSB

resistors has 1⁄64 of the total reference voltage across it. Tap

points are found between all of the resistors in both the MSB

and LSB ladders. The Comparator MultipIexer can connect

any of these tap points, in two adjacent groups of eight, to

the sixteen comparators shown at the right of Figure 4. This

function provides the necessary reference voltages to the

comparators during the first two flash conversions.

The six comparators, seven-resistor string (Estimator DAC

ladder), and Estimator Decoder at the left of Figure 4 form

the Voltage Estimator. The Estimator DAC, connected be-

tween VREF+ and VREF−, generates the reference voltages

for the six Voltage Estimator comparators. The comparators

perform a very low resoIution A/D conversion to obtain an

“estimate” of the input voltage. This estimate is used to con-

trol the placement of the Comparator Multiplexer, connecting

the appropriate MSB ladder section to the sixteen flash com-

parators. A total of only 22 comparators (6 in the Voltage Es-

timator and 16 in the flash converter) is required to quantize

the input to 6 bits, instead of the 64 that would be required

using a traditional 6-bit flash.

Prior to a conversion, the Sample/Hold switch is closed, al-

lowing the voltage on the S/H capacitor to track the input

voItage. Switch 1 is in position 1. A conversion begins by

opening the Sample/Hold switch and latching the output of

the Voltage Estimator. The estimator decoder then selects

two adjacent banks of tap points aIong the MSB ladder.

These sixteen tap points are then connected to the sixteen

flash converters. For exampIe, if the input voltage is between

5/16 and 7/16 of VREF (VREF = VREF+ − VREF−), the estimator

decoder instructs the comparator multiplexer to select the

sixteen tap points between 2/8 and 4/8 (4/16 and 8/16) of

VREF and connects them to the sixteen flash converters. The

first flash conversion is now performed, producing the first 6

MSBs of data.

At this point, Voltage Estimator errors as large as 1/16 of

VREF will be corrected since the flash converters are con-

nected to ladder voltages that extend beyond the range

specified by the Voltage Estimator. For example, if (7/

16)VREF < VIN < (9/16)VREF, the Voltage Estimator’s com-

parators tied to the tap points below (9/16)VREF will output

“1”s (000111). This is decoded by the estimator decoder to

“10”. The 16 comparators will be placed on the MSB ladder

tap points between (3⁄8)VREF and (5⁄8)VREF. This overlap of

(1/16)VREF will automatically cancel a Voltage Estimator er-

ror of up to 256 LSBs. If the first flash conversion determines

that the input voltage is between (3⁄8)VREF and ((4/8)VREF −

LSB/2), the Voltage Estimator’s output code will be corrected

by subtracting “1”, resulting in a corrected value of “01” for

the first two MSBs. If the first flash conversion determines

that the input voltage is between (4/8)VREF − LSB/2) and

(5⁄8)VREF, the voltage estimator’s output code is unchanged.

The results of the first flash and the Voltage Estimator’s out-

put are given to the factory-programmed on-chip EEPROM

which returns a correction code corresponding to the error of

the MSB ladder at that tap. This code is converted to a volt-

age by the Correction DAC. To generate the next four bits,

SW1 is moved to position 2, so the ladder voltage and the

correction voltage are subtracted from the input voltage. The

remainder is applied to the sixteen flash converters and

compared with the 16 tap points from the LSB ladder.

The result of this second conversion is accurate to 10 bits

and describes the input remainder as a voltage between two

tap points (VH and VL) on the LSB ladder. To resolve the last

two bits, the voltage across the ladder resistor (between VH

and VL) is divided up into 4 equal parts by the capacitive volt-

age divider, shown in Figure 5. The divider also creates 6

LSBs below VL and 6 LSBs above VH to provide overlap

used by the digital error correction. SW1 is moved to position

3, and the remainder is compared with these 16 new volt-

ages. The output is combined with the results of the Voltage

Estimator, first flash, and second flash to yield the final 12-bit

result.

By using the same sixteen comparators for all three flash

conversions, the number of comparators needed by the

multi-step converter is significantly reduced when compared

to standard multi-step techniques.

Applications Information

MODES OF OPERATION

The ADC12762 has two interface modes: An interrupt/read

mode and a high speed mode. Figure 1 and Figure 2 show

the timing diagrams for these interfaces.

In order to clearly show the relationship between S/H, CS,

RD, and OE, the control logic decoding section of the

ADC12762 is shown in Figure 6.

Interrupt Interface

As shown in Figure 1, the falling edge of S/H holds the input

voltage and initiates a conversion. At the end of the conver-

sion, the EOC output goes high and the INT output goes low,

indicating that the conversion results are latched and may be

read by pulling RD low. The falling edge of RD resets the INT

line. Note that CS must be low to enable S/H or RD.

High Speed Interface

The Interrupt interface works well at lower speeds, but few

microprocessors could keep up with the 1 µs interrupts that

would be generated if the ADC12762 was running at full

speed. The most efficient interface is shown in Figure 2.

Here the output data is always present on the databus, and

the INT to RD delay is eliminated.

11 www.national.com

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet ADC12762CCV.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADC12762CCV | 12-Bit/ 1.4 MHz/ 300 mW A/D Converter with Input Multiplexer and Sample/Hold | National Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |