|

|

PDF ACT-5260PC-133P10I Data sheet ( Hoja de datos )

| Número de pieza | ACT-5260PC-133P10I | |

| Descripción | ACT5260 64-Bit Superscaler Microprocessor | |

| Fabricantes | Aeroflex Circuit Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ACT-5260PC-133P10I (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

ACT5260

64-Bit Superscaler Microprocessor

Features

s Full militarized QED RM5260 microprocessor

s Dual Issue superscalar QED RISCMark™ - can issue one

integer and one floating-point instruction per cycle

microprocessor - can issue one integer and one

floating-point instruction per cycle

q 100, 133 and 150MHz frequency (200MHz future option)

Consult Factory for latest speeds

q 260 Dhrystone2.1 MIPS

q SPECInt95 4.8. SPECfp95 5.1

s High performance system interface compatible with R4600,

R4700 and R5000

q 64-bit multiplexed system address/data bus for optimum

price/performance up to 100 MHz operating frequency

q High performance write protocols maximize uncached

write bandwidth

q Operates at input system clock multipliers of 2 through 8

q 5V tolerant I/O's

q IEEE 1149.1 JTAG boundary scan

s Integrated on-chip caches - up to 3.2GBps internal data rate

q 16KB instruction - 2 way set associative

q 16KB data - 2 way set associative

q Virtually indexed, physically tagged

q Write-back and write-through on per page basis

q Pipeline restart on first double for data cache misses

s Integrated memory management unit

q Fully associative joint TLB (shared by I and D translations)

q 48 dual entries map 96 pages

q Variable page size (4KB to 16MB in 4x increments)

s Embedded supply de-coupling capacitors and Pll filter

components

s High-performance floating point unit - up to 400 MFLOPS

q Single cycle repeat rate for common single precision

operations and some double precision operations

q Two cycle repeat rate for double precision multiply and

double precision combined multiply-add operations

q Single cycle repeat rate for single precision combined

multiply-add operation

s MIPS IV instruction set

q Floating point multiply-add instruction increases

performance in signal processing and graphics

applications

q Conditional moves to reduce branch frequency

q Index address modes (register + register)

s Embedded application enhancements

q Specialized DSP integer Multiply-Accumulate instruction

and 3 operand multiply instruction

q I and D cache locking by set

q Optional dedicated exception vector for interrupts

s Fully static CMOS design with power down logic

q Standby reduced power mode with WAIT instruction

q 5 Watts typical at 3.3V, less than 175 mwatts in Standby

s 208-lead CQFP, cavity-up package (F17)

s 208-lead CQFP, inverted footprint (F24), Intended to duplicate

the commercial QED footprint (Consult Factory)

s 179-pin PGA package (Future Product) (P10)

BLOCK DIAGRAM

Data Set A

Store Buffer

Phase Lock Loop

Data Tag A

DTLB Physical

Data Tag B

Sys AD

Instruction Set A

Instruction Select

Write Buffer

Read Buffer

Data Set B

Address Buffer

Instruction Tag A

ITLB Physical

Instruction Tag B

Integer Instruction Register

FP Instruction Register

Instruction Set B

Control

DBus

Floating-point

Register File

Unpacker/Packer

Floating-point

MAdd, Add, Sub,Cvt

Div, SqRt

FPIBus

Tag Aux Tag

Joint TLB

Coprocessor 0

System/Memory

Control

DVA

IVA

PC Incrementer

Branch Adder

Instruction TLB Virtual

Program Counter

IntIBus

Load Aligner

Integer Register File

Integer/Address Adder

Data TLB Virtual

Shifter/Store Aligner

Logic Unit

ABus

Integer Multiply, Divide

eroflex Circuit Technology – RISC TurboEngines For The Future © SCD5260 REV A 3/29/99

1 page

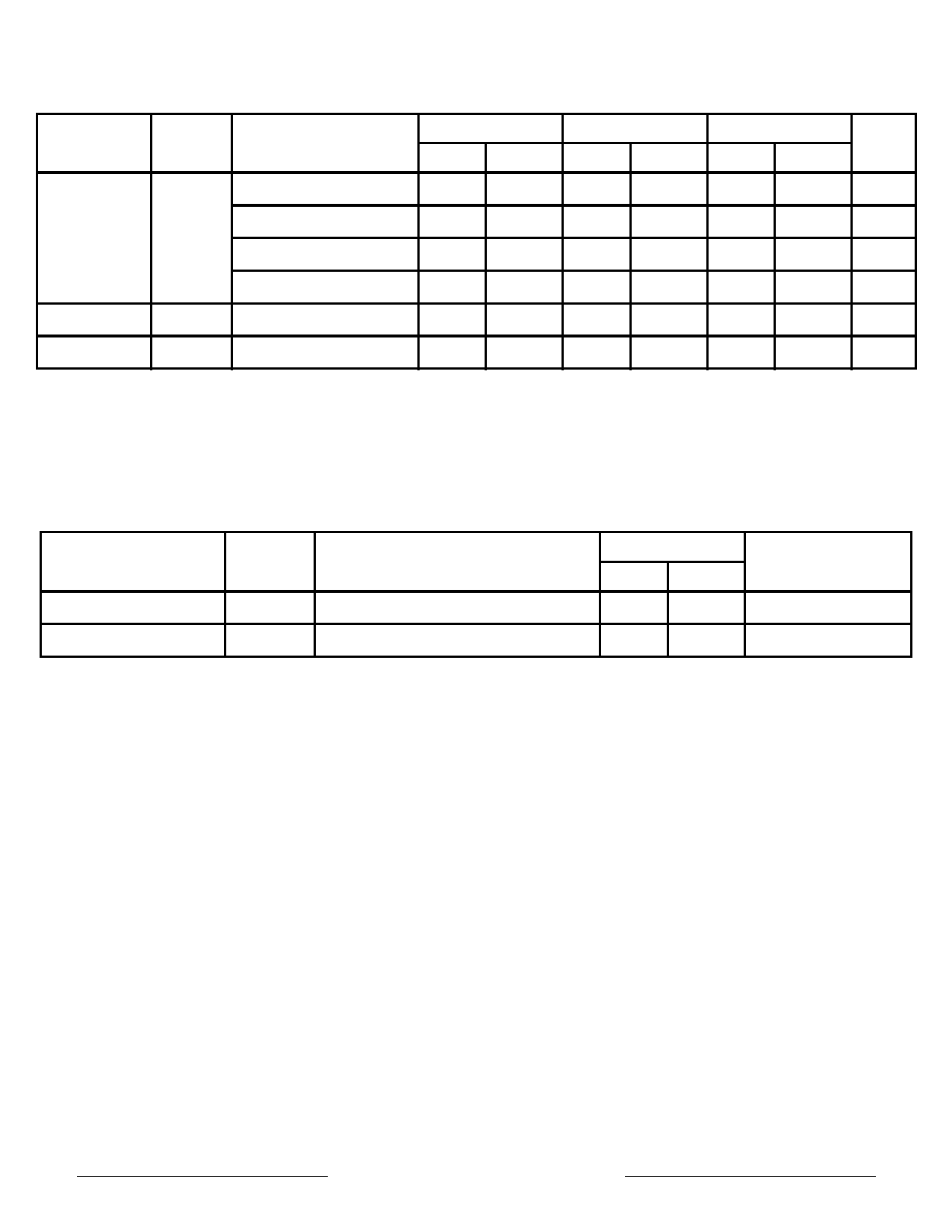

System Interface Parameters7

Parameter

Symbol

Test Conditions

100MHz

Min Max

Data Output8

mode14...13 = 10 (fastest) 1.0

7.0

mode14...13 = 11

tDO

mode14...13 = 00

1.0 7.5

1.0 8.0

mode14...13 = 01 (slowest) 1.0

8.5

Data Setup

tDS tRISE = 5ns

5.0

Data Hold

tDH tFALL= 5ns

2.0

Notes: -

7. Timmings are are measured from from 1.5V of the clock to 1.5V of the signal.

8. Capacitive load for all output timing is 50pF.

-

-

133MHz

Min Max

1.0 7.0

1.0 7.5

1.0 8.0

1.0 8.5

5.0 -

2.0 -

150MHz

Min Max

1.0 7.0

1.0 7.5

1.0 8.0

1.0 8.5

5.0 -

2.0 -

Units

ns

ns

ns

ns

ns

ns

Parameter

Mode Data Setup

Mode Data Hold

Symbol

tDS

tDH

Boot Time Interface Parameters

Test Conditions

100/133/150MHz

Min Max

4-

0-

Units

SysClock cycles

SysClock cycles

Aeroflex Circuit Technology

5 SCD5260 REV A 3/29/99 Plainview NY (516) 694-6700

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet ACT-5260PC-133P10I.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ACT-5260PC-133P10C | ACT5260 64-Bit Superscaler Microprocessor | Aeroflex Circuit Technology |

| ACT-5260PC-133P10I | ACT5260 64-Bit Superscaler Microprocessor | Aeroflex Circuit Technology |

| ACT-5260PC-133P10M | ACT5260 64-Bit Superscaler Microprocessor | Aeroflex Circuit Technology |

| ACT-5260PC-133P10Q | ACT5260 64-Bit Superscaler Microprocessor | Aeroflex Circuit Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |