|

|

PDF AD1888 Data sheet ( Hoja de datos )

| Número de pieza | AD1888 | |

| Descripción | AC 97 SoundMAX Codec | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD1888 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

a

AC ’97 SoundMAX®Codec

AD1888

FEATURES

AC ’97 2.3 COMPATIBLE FEATURES

6 DAC Channels for 5.1 Surround

90 dB Dynamic Range

20-Bit PCM DACs

S/PDIF Output

Integrated Stereo Headphone Amplifiers

Phone, Aux, and Line-In

High Quality CD Input

Selectable MIC Input

Mono Output

External Amplifier Power-Down Control

Double Rate Audio (fS = 96 kHz)

Power Management Modes

48-Lead LQFP and 48-Lead LFCSP Packages

ENHANCED FEATURES

Selectable Front and Rear MIC Inputs

with Preamp

Integrated PLL for System Clocking

Crystal-Free Operation

Variable Sample Rate 7 kHz to 96 kHz

Jack Sense (Auto Topology Switching)

Software Controlled VREF_OUT for MIC Bias

Software Enabled Outputs for Jack Sharing

Auto Down-Mix and Channel Spreading Modes

FUNCTIONAL BLOCK DIAGRAM

MIC1

MIC2

PHONE_IN

CD_L

CD_R

AUX_L

AUX_R

LINE_IN_L

LINE_IN_R

G

DIFF

AMP

MONO_OUT

MA

LINE_OUT_L

LINE_OUT_R

MZ A

MZ A

CENTER_OUT

LFE_OUT

MZ A

MZ A

SURR_L/

HP_OUT_L

SURR_R/

HP_OUT_R

REV. 0

HP M A

HP M A

AD1888

G

M

16-BIT ⌺-⌬

ADC

G

M

16-BIT ⌺-⌬

ADC

ADC

SLOT

LOGIC

PLL

GA GA

GA

GA

MM

GA

GA

M

M GA

M

GA

M

GA

M

MM

MMMMMM

G = GAIN

A = ATTENUATION

M = MUTE

Z = HIGH-Z

M GA

M GA

20-BIT ⌺-⌬

DAC

20-BIT ⌺-⌬

DAC

M GA

M GA

20-BIT ⌺-⌬

DAC

20-BIT ⌺-⌬

DAC

M GA

M GA

20-BIT ⌺-⌬

DAC

20-BIT ⌺-⌬

DAC

AC '97

CONTROL

REGISTERS

DAC

SLOT

LOGIC

SPDIF

TX

EAPD

JACK

SENSE

LOGIC

VOLTAGE

REFERENCE

XTAL_IN

XTAL_OUT

ID0

ID1

RESET

SYNC

BIT_CLK

SDATA_OUT

SDATA_IN

SPDIF_OUT

EAPD

JS0

JS1

VREF

VREFOUT

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

1 page

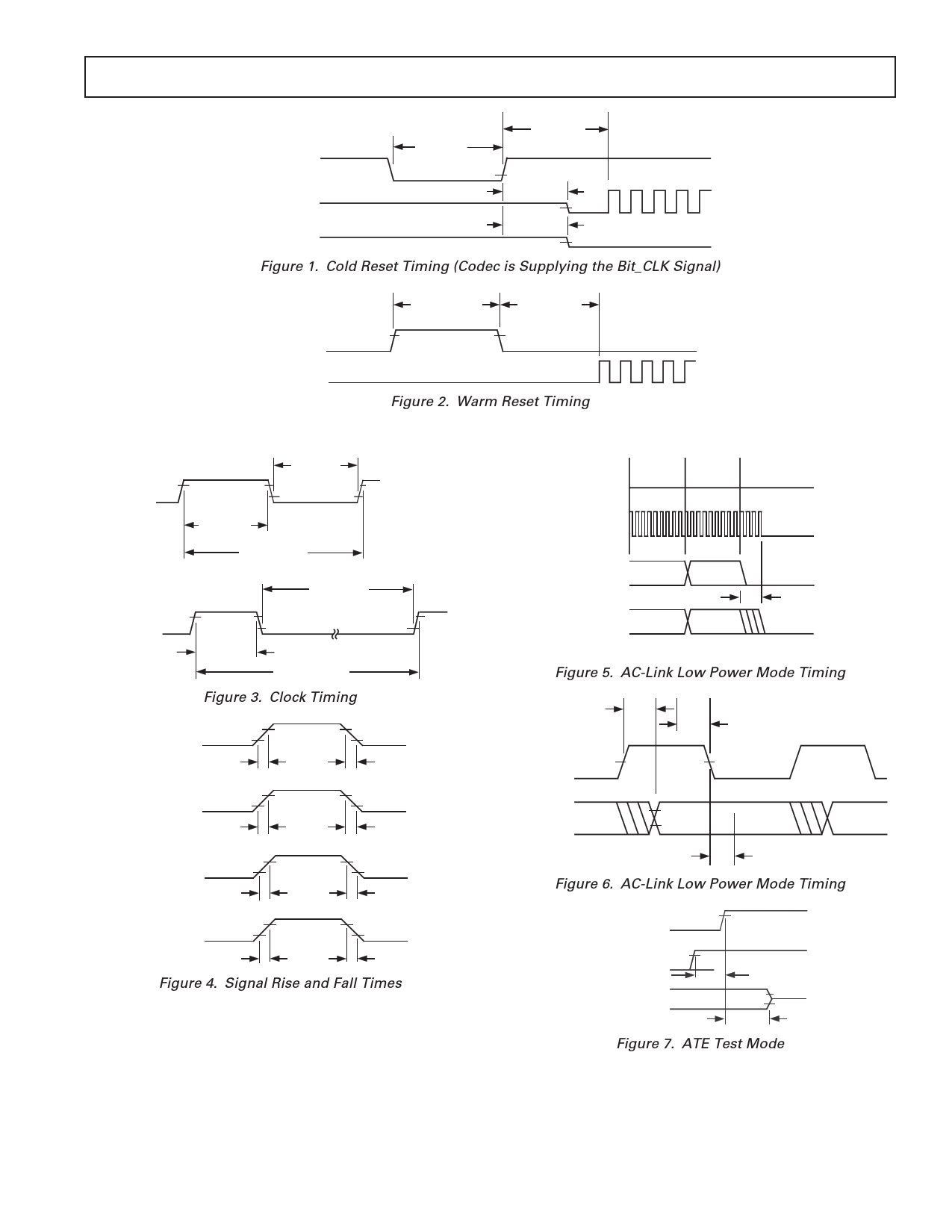

tRST_LOW

tRST2CLK

RESET

BIT_CLK

SDATA_IN

tTRI2ACTV

tTRI2ACTV

Figure 1. Cold Reset Timing (Codec is Supplying the Bit_CLK Signal)

SYNC

BIT_CLK

tSYNC_HIGH

tSYNC2CLK

Figure 2. Warm Reset Timing

AD1888

BIT_CLK

SYNC

tCLK_LOW

tCLK_HIGH

tCLK_PERIOD

tSYNC_LOW

tSYNC_HIGH

tSYNC_PERIOD

Figure 3. Clock Timing

BIT_CLK

tRISECLK

tFALLCLK

SYNC

tRISESYNC

tFALLSYNC

SDATA_IN

tRISEDIN

tFALLDIN

SDATA_OUT

tRISEDOUT

tFALLDOUT

Figure 4. Signal Rise and Fall Times

SLOT 1

SYNC

SLOT 2

BIT_CLK

WRITE TO

SDATA_OUT 0x26

DATA

PR4

SDATA_IN

tS2_PDOWN

BIT_CLK NOT TO SCALE

Figure 5. AC-Link Low Power Mode Timing

tCO

BIT_CLK

VIH

tSETUP

VIL

SDATA_OUT

SDATA_IN

SYNC

VOH

VOL

tHOLD

Figure 6. AC-Link Low Power Mode Timing

RESET

SDATA_OUT

SDATA_IN, BIT_CLK,

EAPD, SPDIF_OUT

AND DIGITAL I/O

tSETUP2RST

tOFF

Hi-Z

Figure 7. ATE Test Mode

REV. 0

–5–

5 Page

AD1888

Headphones Volume Register (Index 04h)

Reg

No. Name

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 Default

04h Headphones HPM X

Volume

LHV5 LHV4 LHV3 LHV2 LHV1 LHV0 HPRM* X RHV5 RHV4 RHV3 RHV2 RHV1 RHV0 8000h

*For AC ’97 compatibility, Bit D7 is available only by setting the MSPLT bit, Register 76h. The MSPLT bit enables separate mute bits for the left and right

channels. If MSPLT is not set, Bit D7 has no effect.

Table I. Volume Settings for Master and Headphone

Reg. 76h

Control Bits

Master Volume (02h) and Headphone Volume (04h)

Left Channel Volume D[13:8]

Right Channel Volume D[5:0]

MSPLT* D15 WRITE READBACK Function

D7* WRITE READBACK Function

0

0 00 0000 00 0000

0 dB Gain

x 00 0000 00 0000

0 dB Gain

0

0 00 1111 00 1111

–22.5 dB Gain

x 00 1111 00 1111

–22.5 dB Gain

0

0 01 1111 01 1111

–46.5 dB Gain

x 01 1111 01 1111

–46.5 dB Gain

0

0 1x xxxx 01 1111

–46.5 dB Gain

x 1x xxxx 01 1111

–46.5 dB Gain

0

1 xx xxxx xx xxxx

–ϱ dB Gain, Muted

x xx xxxx xx xxxx

–ϱ dB Gain, Muted

1

0 1x xxxx 01 1111

–46.5 dB Gain

1 xx xxxx xx xxxx

–ϱ dB Gain, only

Right Muted

1

1 xx xxxx xx xxxx

–ϱ dB Gain, Left only Muted 0 xx xxxx xx xxxx

–46.5 dB Gain

1

1 xx xxxx xx xxxx

–ϱ dB Gain, Left Muted

1 xx xxxx xx xxxx

–ϱ dB Gain, Right

Muted

*For AC ’97 compatibility, Bit D7 is available only by setting the MSPLT bit, Register 76h. The MSPLT bit enables separate mute bits for the left and right

channels. If MSPLT is not set, Bit D7 has no effect.

x in the above table is “don’t care.”

Mono Volume Register (Index 06h)

Reg

No. Name

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5* D4 D3 D2 D1 D0 Default

06h Mono Volume MVM X X X X X X X X X MV5 MV4 MV3 MV2 MV1 MV0 8000h

*Refer to Table II for examples. This register controls the Mono output volume and mute bit. The volume register contains five bits, generating 32 volume levels with

31 steps of 1.5 dB each. Because AC ’97 defines 6-bit volume registers, to maintain compatibility, whenever the D5 bit is set to 1, their respective lower five volume

bits are automatically set to 1 by the codec logic. On readback, all lower five bits will read 1s whenever this bit is set to 1. All registers not shown and bits containing

an X are assumed to be reserved.

MV[5:0]

MVM

Mono Volume Control. The least significant bit represents 1.5 dB. This register controls the output from 0 dB to a

maximum attenuation of 46.5 dB.

Mono Volume Mute. When this bit is set to 1, the channel is muted.

REV. 0

Table II. Volume Settings for Mono

Control Bits D[4:0] for Mono (06h)

D15 WRITE

READBACK

0 0 0000

0 0 1111

0 1 1111

1 x xxxx

0 0000

0 1111

1 1111

x xxxx

x in the above table is a wild card and has no effect on the value.

Function

0 dB Gain

–22.5 dB Gain

–46.5 dB Gain

–ϱ dB Gain, Muted

–11–

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AD1888.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD1881 | AC97 SoundMAX Codec | Analog Devices |

| AD1882 | High Definition Audio SoundMAX Codec | Analog Devices |

| AD1883 | High Definition Audio SoundMAX Codec | Analog Devices |

| AD1884 | High Definition Audio SoundMAX Codec | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |