|

|

PDF AD1833 Data sheet ( Hoja de datos )

| Número de pieza | AD1833 | |

| Descripción | Multichannel 24-Bit/ 192 kHz/ DAC | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD1833 (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

a

Multichannel,

24-Bit, 192 kHz, ⌺-⌬ DAC

AD1833

FEATURES

5 V Stereo Audio System with 3.3 V Tolerant Digital

Interface

Supports 96 kHz Sample Rates on Six Channels and

192 kHz on 2 Channels

Supports 16-/20-/24-Bit Word Lengths

Multibit Sigma-Delta Modulators with

“Perfect Differential Linearity Restoration” for

Reduced Idle Tones and Noise Floor

Data Directed Scrambling DACs—Least Sensitive to

Jitter

Differential Output for Optimum Performance

DACs Signal-to-Noise and Dynamic Range: 110 dB

–94 dB THD + N—6-Channel Mode

–95 dB THD + N—2-Channel Mode

On-Chip Volume Control Per Channel with 1024-Step

Linear Scale

Software Controllable Clickless Mute

Digital De-Emphasis Processing

Supports 256 ؋ fS, 512؋ fS, and 768؋ fS Master

Clock Modes

Power-Down Mode Plus Soft Power-Down Mode

Flexible Serial Data Port with Right-Justified, Left-

Justified, I2S-Compatible and DSP Serial Port Modes

Supports Packed Data Mode (TDM) for DACs

48-Lead LQFP Plastic Package

APPLICATIONS

DVD Video and Audio Players

Home Theatre Systems

Automotive Audio Systems

Set-Top Boxes

Digital Audio Effects Processors

GENERAL DESCRIPTION

The AD1833 is a complete, high-performance, single-chip, multi-

channel, digital audio playback system. It features six audio

playback channels each comprising a high-performance digital

interpolation filter, a multibit sigma-delta modulator featuring

Analog Devices patented technology and a continuous-time

voltage-out analog DAC section. Other features include an on-chip

clickless attenuator and mute capability, per channel, programmed

through an SPI-compatible serial control port.

FUNCTIONAL BLOCK DIAGRAM

DVDD1 DVDD2

ZERO FLAGS

AVDD

CDATA

CLATCH

CCLK

MCLK

RESET

L/RCLK

BCLK

SDIN1

SDIN2

SDIN3

SOUT

SPI

PORT

INTERPOLATOR

DAC

INTERPOLATOR

DAC

FILTER

ENGINE

INTERPOLATOR

INTERPOLATOR

DAC

DAC

DATA

PORT

INTERPOLATOR

DAC

AD1833

INTERPOLATOR

DAC

DGND

FILTR FILTD

AGND

OUTLP1

OUTLN1

OUTLP2

OUTLN2

OUTLP3

OUTLN3

OUTRP3

OUTRN3

OUTRP2

OUTRN2

OUTRP1

OUTRN1

The AD1833 is fully compatible with all known DVD formats,

catering for up to 24-bit word lengths at sample rates of 48 kHz

and 96 kHz on all six channels while supporting a 192 kHz

sample rate on two channels. It also provides the “Redbook”

standard 50 µs/15 µs digital de-emphasis filters at sample rates

of 32 kHz, 44.1 kHz, and 48 kHz.

The AD1833 has a very flexible serial data input port that allows

for glueless interconnection to a variety of ADCs, DSP chips,

AES/EBU receivers, and sample rate converters. The AD1833

can be configured in left-justified, I2S, right-justified, or DSP

serial port compatible modes. The AD1833 accepts serial audio

data in MSB first, two’s complement format. While the AD1833

can be operated from a single 5 V power supply, it also features

a separate supply pin for its digital interface which allows the

device to be interfaced to devices using 3.3 V power supplies.

It is fabricated on a single monolithic integrated circuit and is

housed in a 48-lead LQFP package for operation over the tem-

perature range –40°C to +85°C.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2001

1 page

CDATA

CCLK

CLATCH

Pin

1

2

3, 4, 33, 34, 44

5, 6, 7, 30, 31, 32, 41

8, 29

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

35

36

37

38

39

40

42

43

45

46

47

48

REV. 0

D15

t CCH

t CHD

D14

AD1833

D0

t CCL

t CSU

Mnemonic

OUTLP1

OUTLN1

AVDD

AGND

DGND

DVDD1

ZEROA

ZERO3R

ZERO3L

ZERO2R

CLATCH

CDATA

CCLK

L/RCLK

BCLK

MCLK

SDIN1

SDIN2

SDIN3

SOUT

ZERO2L

ZERO1R

ZERO1L

RESET

DVDD2

OUTRN1

OUTRP1

OUTRN2

OUTRP2

OUTRN3

OUTRP3

FILTR

FILTD

OUTLP3

OUTLN3

OUTLP2

OUTLN2

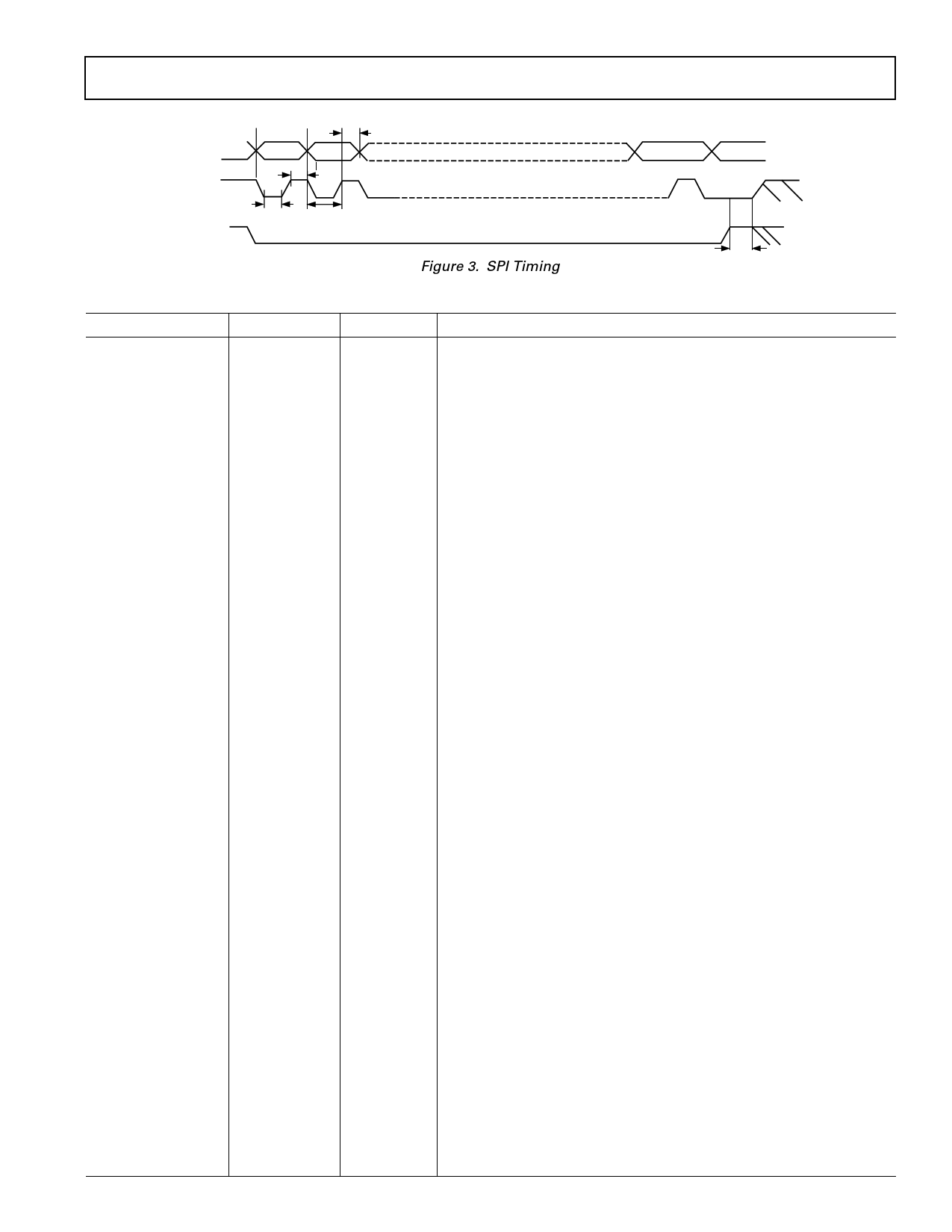

Figure 3. SPI Timing

t CLH

PIN FUNCTION DESCRIPTIONS

IN/OUT

O

O

O

O

O

O

I

I

I

I/O

I/O

I

I

I/O

I/O

O

O

O

O

I

O

O

O

O

O

O

O

O

O

O

Description

DAC 1 Left Channel Positive Output.

DAC 1 Left Channel Negative Output.

Analog Supply.

Analog Ground.

Digital Ground.

Digital Supply to Core Logic.

Flag to Indicate Zero Input on All Channels.

Flag to Indicate Zero Input on Channel 3 Right.

Flag to Indicate Zero Input on Channel 3 Left.

Flag to Indicate Zero Input on Channel 2 Right.

Latch Input for Control Data (SPI Port).

Serial Control Data Input (SPI Port).

Clock Input for Control Data (SPI Port).

Left/Right Clock for DAC Data Input (FSTDM Output in TDM Mode).

Bit Clock for DAC Data Input (BCLKTDM Output in TDM Mode).

Master Clock Input.

Data Input for Channel 1 Left/Right (Data Stream Input in TDM

and Packed Modes).

Data Input for Channel 2 Left/Right (L/RCLK Output to Auxiliary

DAC in TDM Mode).

Data Input for Channel 3 Left/Right (BCLK Output to Auxiliary

DAC in TDM Mode).

Auxiliary I2S Output (Available in TDM Mode).

Flag to Indicate Zero Input on Channel 2 Left.

Flag to Indicate Zero Input on Channel 1 Right.

Flag to Indicate Zero Input on Channel 1 Left.

Power-Down and Reset Control.

Power Supply to External Interface Logic.

DAC 1 Right Channel Negative Output.

DAC 1 Right Channel Positive Output.

DAC 2 Right Channel Negative Output.

DAC 2 Right Channel Positive Output.

DAC 3 Right Channel Negative Output.

DAC 3 Right Channel Positive Output.

Reference/Filter Capacitor Connection. Recommend 10 µF/100 µF

Decouple to Analog Ground.

Filter Capacitor Connection. Recommend 10 µF/100 µF Decouple to

Analog Ground.

DAC 3 Left Channel Positive Output.

DAC 3 Left Channel Negative Output.

DAC 2 Left Channel Positive Output.

DAC 2 Left Channel Negative Output.

–5–

5 Page

MCLK Select

The AD1833 allows the matching of available external MCLK

frequencies to the required sample rate. The oversampling rate

can be selected from 256 × fS, 512 × fS or 768 × fS by writing to

Bit 4 and Bit 3. Internally the AD1833 requires an MCLK of

512 × fS; therefore, in the case of 256 × fS mode, a clock doubler

is used, whereas in 768 × fS mode, a divide-by-3 block (/3) is

first implemented, followed by a clock doubler. See Table XII.

Bit 4

0

0

1

1

Table XII. MCLK Settings

Bit 3

0

1

0

1

Oversample Ratio

256 × fS (MCLK × 2 Internally)

512 × fS

768 × fS (MCLK × 2/3 Internally)

Reserved

Channel Zero Status

The AD1833 provides individual logic output status indicators

when zero data is sent to a channel for 1024 or more consecutive

sample periods. There is also a global zero flag that indicates all

channels contain zero data. The polarity of the active zero signal

AD1833

is programmable by writing to Control Bit 2, see Table XIII.

The six individual channel flags are best used as three stereo

zero flags by combining pairs of them through suitable logic

gates. Then, when both the left and right input are zero for 1024

clock cycles, i.e., a stereo zero input for 1024 sample periods,

the combined result of the two individual flags will go active

indicating a stereo zero.

Table XIII. Zero Detect

Bit 2

0

1

Channel Zero Status

Active High

Active Low

DAC Volume Control Registers

The AD1833 has six volume control registers, one each for the

six DAC channels. Volume control is exercised by writing to the

relevant register associated with each DAC. This setting is used

to attenuate the DAC output. Full-scale setting (all 1s) is equiva-

lent to zero attenuation. See Table XV.

Sampling Rate fS (kHz)

32

64

128

44.1

88.2

176.4

48

96

192

Table XIV. MCLK vs. Sample Rate Selection

Interpolator Mode

8× (Normal)

4× (Double)

2× (4 Times)

8× (Normal)

4× (Double)

2× (4 Times)

8× (Normal)

4× (Double)

2× (4 Times)

256 fS

8.192

11.2896

12.288

MCLK (MHz)

512 fS

16.384

22.5792

24.576

768 fS

24.576

33.8688

36.864

Table XV. Volume Control Registers

Address

Reserved*

15–12

11 10

0010

0011

0100

0101

0110

0111

0

0

*Must be programmed to zero.

Volume Control

9–0

Channel 1 Volume Control (OUTL1)

Channel 2 Volume Control (OUTR1)

Channel 3 Volume Control (OUTL2)

Channel 4 Volume Control (OUTR2)

Channel 5 Volume Control (OUTL3)

Channel 6 Volume Control (OUTR3)

REV. 0

–11–

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet AD1833.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD1833 | Multichannel 24-Bit/ 192 kHz/ DAC | Analog Devices |

| AD1833A | 24-Bit/ 192 kHz/ DAC | Analog Devices |

| AD1835 | 2 ADC/ 8 DAC/ 96 kHz/ 24-Bit Codec | Analog Devices |

| AD1835A | Codecs | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |