|

|

PDF AD5340 Data sheet ( Hoja de datos )

| Número de pieza | AD5340 | |

| Descripción | Parallel Interface Single Voltage-Output 8-/10-/12-Bit DACs | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD5340 (archivo pdf) en la parte inferior de esta página. Total 28 Páginas | ||

|

No Preview Available !

2.5 V to 5.5 V, 115 μA, Parallel Interface

Single Voltage-Output 8-/10-/12-Bit DACs

AD5330/AD5331/AD5340/AD5341

FEATURES

GENERAL DESCRIPTION

AD5330: single 8-bit DAC in 20-lead TSSOP

AD5331: single 10-bit DAC in 20-lead TSSOP

AD5340: single 12-bit DAC in 24-lead TSSOP

AD5341: single 12-bit DAC in 20-lead TSSOP

Low power operation: 115 μA @ 3 V, 140 μA @ 5 V

Power-down to 80 nA @ 3 V, 200 nA @ 5 V via PD Pin

2.5 V to 5.5 V power supply

Double-buffered input logic

Guaranteed monotonic by design over all codes

Buffered/unbuffered reference input options

Output range: 0 V to VREF or 0 V to 2 × VREF

Power-on reset to 0 V

Simultaneous update of DAC outputs via LDAC pin

Asynchronous CLR facility

Low power parallel data interface

On-chip rail-to-rail output buffer amplifiers

Temperature range: −40°C to +105°C

APPLICATIONS

Portable battery-powered instruments

Digital gain and offset adjustment

Programmable voltage and current sources

Programmable attenuators

Industrial process control

The AD5330/AD5331/AD5340/AD53411 are single 8-/10-/12-

bit DACs. They operate from a 2.5 V to 5.5 V supply consuming

just 115 μA at 3 V and feature a power-down mode that further

reduces the current to 80 nA. The devices incorporate an on-chip

output buffer that can drive the output to both supply rails, but

the AD5330, AD5340, and AD5341 allow a choice of buffered

or unbuffered reference input.

The AD5330/AD5331/AD5340/AD5341 have a parallel

interface. CS selects the device and data is loaded into the

input registers on the rising edge of WR.

The GAIN pin allows the output range to be set at 0 V to VREF or

0 V to 2 × VREF.

Input data to the DACs is double-buffered, allowing simultane-

ous update of multiple DACs in a system using the LDAC pin.

An asynchronous CLR input is also provided, which resets the

contents of the input register and the DAC register to all zeros.

These devices also incorporate a power-on reset circuit that

ensures that the DAC output powers on to 0 V and remains

there until valid data is written to the device.

The AD5330/AD5331/AD5340/AD5341 are available in thin

shrink small outline packages (TSSOP).

1 Protected by U.S. Patent Number 5,969,657.

FUNCTIONAL BLOCK DIAGRAM

VREF

3

VDD

12

POWER-ON

RESET

AD5330

BUF 1

GAIN 8

DB.. 7 20

DB0 13

CS 6

WR 7

CLR 9

LDAC 10

INPUT

REGISTER

DAC

REGISTER

8-BIT

DAC

BUFFER

4 VOUT

RESET

POWER-DOWN

LOGIC

Figure 1. AD5330

11 5

PD GND

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113 ©2000–2008 Analog Devices, Inc. All rights reserved.

1 page

AD5330/AD5331/AD5340/AD5341

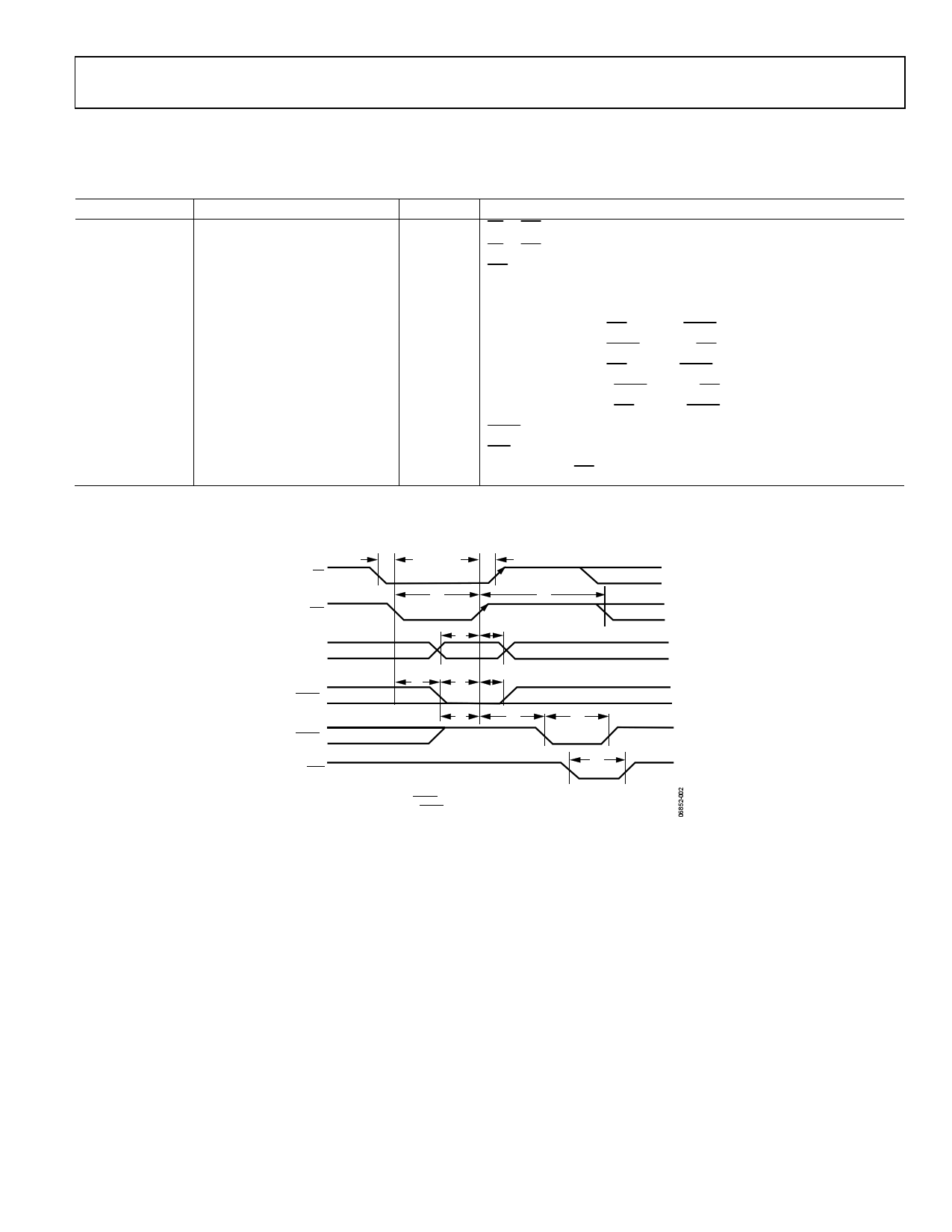

TIMING CHARACTERISTICS1, 2, 3

VDD = 2.5 V to 5.5 V, all specifications TMIN to TMAX, unless otherwise noted.

Table 3.

Parameter

t1

t2

t3

t4

t5

t6

t7

t8

t9

t10

t11

t12

t13

Limit at TMIN, TMAX

0

0

20

5

4.5

5

5

4.5

5

4.5

20

20

50

Unit

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns min

Condition/Comments

CS to WR setup time.

CS to WR hold time.

WR pulse width.

Data, GAIN, BUF, HBEN setup time.

Data, GAIN, BUF, HBEN hold time.

Synchronous mode; WR falling to LDAC falling.

Synchronous mode; LDAC falling to WR rising.

Synchronous mode; WR rising to LDAC rising.

Asynchronous mode; LDAC rising to WR rising.

Asynchronous mode; WR rising to LDAC falling.

LDAC pulse width.

CLR pulse width.

Time between WR cycles.

1 Guaranteed by design and characterization, not production tested.

2 All input signals are specified with tR = tF = 5 ns (10% to 90% of VDD) and timed from a voltage level of (VIL + VIH)/2.

3 See Figure 2.

CS

WR

DATA,

GAIN,

BUF,

HBEN

LDAC1

LDAC2

t1 t2

t3

t4 t5

t13

t6 t7 t8

t9 t10

t11

CLR

t12

NOTES:

1SYNCHRONOUS LDAC UPDATE MODE

2ASYNCHRONOUS LDAC UPDATE MODE

Figure 2. Parallel Interface Timing Diagram

Rev. A | Page 5 of 28

5 Page

TERMINOLOGY

Relative Accuracy or Integral Nonlinearity (INL)

For the DAC, relative accuracy or INL is a measure of the

maximum deviation, in LSBs, from a straight line passing

through the actual endpoints of the DAC transfer function.

Typical INL vs. code plots can be seen in Figure 14, Figure 15,

and Figure 16.

Differential Nonlinearity (DNL)

DNL is the difference between the measured change and the

ideal 1 LSB change between any two adjacent codes. A specified

differential nonlinearity of ±1 LSB maximum ensures mono-

tonicity. This DAC is guaranteed monotonic by design. Typical

DNL vs. code plots can be seen in Figure 17, Figure 18, and

Figure 19.

Gain Error

This is a measure of the span error of the DAC (including any

error in the gain of the buffer amplifier). It is the deviation in

slope of the actual DAC transfer characteristic from the ideal,

expressed as a percentage of the full-scale range. This is

illustrated in Figure 11.

Offset Error

This is a measure of the offset error of the DAC and the output

amplifier. It is expressed as a percentage of the full-scale range.

If the offset voltage is positive, the output voltage is still positive

at zero input code. This is shown in Figure 12. Because the

DACs operate from a single supply, a negative offset cannot

appear at the output of the buffer amplifier. Instead, there is

a code close to zero at which the amplifier output saturates

(amplifier footroom). Below this code, there is a deadband over

which the output voltage does not change. This is illustrated in

Figure 13.

POSITIVE

GAIN ERROR

NEGATIVE

GAIN ERROR

OUTPUT

VOLTAGE

ACTUAL

IDEAL

AD5330/AD5331/AD5340/AD5341

OUTPUT

VOLTAGE

GAIN ERROR

AND

OFFSET ERROR

ACTUAL

IDEAL

POSITIVE

OFFSET

DAC CODE

Figure 12. Positive Offset Error and Gain Error

OUTPUT

VOLTAGE

GAIN ERROR

AND

OFFSET ERROR

ACTUAL

IDEAL

NEGATIVE

OFFSET

DAC CODE

AMPLIFIER

FOOTROOM

(~1mV)

DEADBAND CODES

NEGATIVE

OFFSET

DAC CODE

Figure 11. Gain Error

Figure 13. Negative Offset Error and Gain Error

Rev. A | Page 11 of 28

11 Page | ||

| Páginas | Total 28 Páginas | |

| PDF Descargar | [ Datasheet AD5340.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD534 | Internally Trimmed Precision IC Multiplier | Analog Devices |

| AD5340 | Parallel Interface Single Voltage-Output 8-/10-/12-Bit DACs | Analog Devices |

| AD5341 | Parallel Interface Single Voltage-Output 8-/10-/12-Bit DACs | Analog Devices |

| AD5342 | Parallel Interface Dual Voltage-Output 8-/10-/12-Bit DACs | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |