|

|

PDF AD7894 Data sheet ( Hoja de datos )

| Número de pieza | AD7894 | |

| Descripción | 5 V/ 14-Bit Serial/ 5 ms ADC in SO-8 Package | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD7894 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

a

FEATURES

Fast 14-Bit ADC with 5 s Conversion Time

8-Lead SOIC Package

Single 5 V Supply Operation

High Speed, Easy-to-Use, Serial Interface

On-Chip Track/Hold Amplifier

Selection of Input Ranges

؎10 V for AD7894-10

؎2.5 V for AD7894-3

0 V to +2.5 V for AD7894-2

High Input Impedance

Low Power: 20 mW Typ

Pin Compatible Upgrade of 12-Bit AD7895

5 V, 14-Bit Serial, 5 s

ADC in SO-8 Package

AD7894

FUNCTIONAL BLOCK DIAGRAM

REF IN

VDD

AD7894

TRACK/

VIN

SIGNAL

SCALING*

HOLD

14-BIT

ADC

CONVST

OUTPUT

REGISTER

GENERAL DESCRIPTION

The AD7894 is a fast, 14-bit ADC that operates from a single

+5 V supply and is housed in a small 8-lead SOIC. The part

contains a 5 µs successive approximation A/D converter, an on-

chip track/hold amplifier, an on-chip clock and a high speed

serial interface.

Output data from the AD7894 is provided via a high speed,

serial interface port. This two-wire serial interface has a serial

clock input and a serial data output with the external serial clock

accessing the serial data from the part.

In addition to the traditional dc accuracy specifications such as

linearity, full-scale and offset errors, the AD7894 is also speci-

fied for dynamic performance parameters including harmonic

distortion and signal-to-noise ratio.

The part accepts an analog input range of ± 10 V (AD7894-10),

± 2.5 V (AD7894-3), 0 V to +2.5 V (AD7894-2), and operates

from a single +5 V supply consuming only 20 mW typical.

The AD7894 features a high sampling rate mode and, for low

power applications, a proprietary automatic power-down mode

where the part automatically goes into power-down once conver-

sion is complete and “wakes up” before the next conversion

cycle.

The part is available in a small outline IC (SOIC).

GND

BUSY

*AD7894-10, AD7894-3

SCLK SDATA

PRODUCT HIGHLIGHTS

1. Fast, 14-Bit ADC in 8-Lead Package

The AD7894 contains a 5␣ µs ADC, a track/hold amplifier,

control logic and a high speed serial interface, all in an 8-lead

package. This offers considerable space saving over alterna-

tive solutions.

2. Low Power, Single Supply Operation

The AD7894 operates from a single +5 V supply and con-

sumes only 20 mW. The automatic power-down mode,

where the part goes into power-down once conversion is

complete and “wakes up” before the next conversion cycle,

makes the AD7894 ideal for battery powered or portable

applications.

3. High Speed Serial Interface

The part provides high speed serial data and serial clock lines

allowing for an easy, two-wire serial interface arrangement.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 1998

1 page

AD7894

TERMINOLOGY

Signal to (Noise + Distortion) Ratio

This is the measured ratio of signal to (noise + distortion) at the

output of the A/D converter. The signal is the rms amplitude of

the fundamental. Noise is the rms sum of all nonfundamental

signals up to half the sampling frequency (fS/2), excluding dc.

The ratio is dependent upon the number of quantization levels

in the digitization process; the more levels, the smaller the quan-

tization noise. The theoretical signal to (noise + distortion) ratio

for an ideal N-bit converter with a sine wave input is given by:

Signal to (Noise + Distortion) = (6.02␣ N + 1.76) dB

Thus for a 14-bit converter, this is 86.04 dB.

Total Harmonic Distortion

Total harmonic distortion (THD) is the ratio of the rms sum of

harmonics to the fundamental. For the AD7894, it is defined as:

THD (dB) = 20 log V22 +V32 +V42 +V52 +V62

V1

where V1 is the rms amplitude of the fundamental and V2, V3,

V4, V5 and V6 are the rms amplitudes of the second through the

sixth harmonics.

Peak Harmonic or Spurious Noise

Peak harmonic or spurious noise is defined as the ratio of the

rms value of the next largest component in the ADC output

spectrum (up to fS/2 and excluding dc) to the rms value of the

fundamental. The value of this specification is normally deter-

mined by the largest harmonic in the spectrum, but for parts

where the harmonics are buried in the noise floor, it will be a

noise peak.

Intermodulation Distortion

With inputs consisting of sine waves at two frequencies, fa and

fb, any active device with nonlinearities will create distortion

products at sum and difference frequencies of mfa ± nfb where

m, n = 0, 1, 2, 3, etc. Intermodulation terms are those for which

neither m nor n is equal to zero. For example, the second order

terms include (fa + fb) and (fa – fb), while the third order terms

include (2 fa + fb), (2 fa – fb), (fa + 2 fb) and (fa – 2 fb).

The AD7894 is tested using two input frequencies. In this case,

the second and third order terms are of different significance.

The second order terms are usually distanced in frequency from

the original sine waves, while the third order terms are usually at

a frequency close to the input frequencies. As a result, the second

and third order terms are specified separately. The calculation

of the intermodulation distortion is as per the THD specification

where it is the ratio of the rms sum of the individual distortion

products to the rms amplitude of the fundamental expressed

in dBs.

Relative Accuracy

Relative accuracy or endpoint nonlinearity is the maximum

deviation from a straight line passing through the endpoints of

the ADC transfer function.

Differential Nonlinearity

This is the difference between the measured and the ideal 1␣ LSB

change between any two adjacent codes in the ADC.

Positive Gain Error (AD7894-10)

This is the deviation of the last code transition (01 . . . 110 to

01 . . . 111) from the ideal (4 × VREF – 1 LSB) after the

Bipolar Zero Error has been adjusted out.

Positive Gain Error (AD7894-3)

This is the deviation of the last code transition (01 . . . 110 to

01 . . . 111) from the ideal (VREF – 1 LSB) after the Bipolar

Zero Error has been adjusted out.

Positive Gain Error (AD7894-2)

This is the deviation of the last code transition (11 . . . 110 to

11 . . . 111) from the ideal (VREF – 1 LSB) after the Unipolar

Offset Error has been adjusted out.

Bipolar Zero Error (AD7894-10, AD7894-3)

This is the deviation of the midscale transition (all 0s to all 1s)

from the ideal 0 V (GND).

Unipolar Offset Error (AD7894-2)

This is the deviation of the first code transition (00 . . . 000 to

00 . . . 001) from the ideal 1 LSB.

Negative Gain Error (AD7894-10)

This is the deviation of the first code transition (10 . . . 000 to

10 . . . 001) from the ideal (–4 × VREF + 1 LSB) after Bipolar

Zero Error has been adjusted out.

Negative Gain Error (AD7894-3)

This is the deviation of the first code transition (10 . . . 000 to

10 . . . 001) from the ideal (– VREF + 1 LSB) after Bipolar

Zero Error has been adjusted out.

Track/Hold Acquisition Time

Track/Hold acquisition time is the time required for the output

of the track/hold amplifier to reach its final value, within

± 1/2␣ LSB, after the end of conversion (the point at which the

track/hold returns to track mode). It also applies to situations

where there is a step input change on the input voltage applied

to the VIN input of the AD7894. This means that the user must

wait for the duration of the track/hold acquisition time after the

end of conversion or after a step input change to VIN before

starting another conversion, to ensure that the part operates to

specification.

REV. 0

–5–

5 Page

AD7894

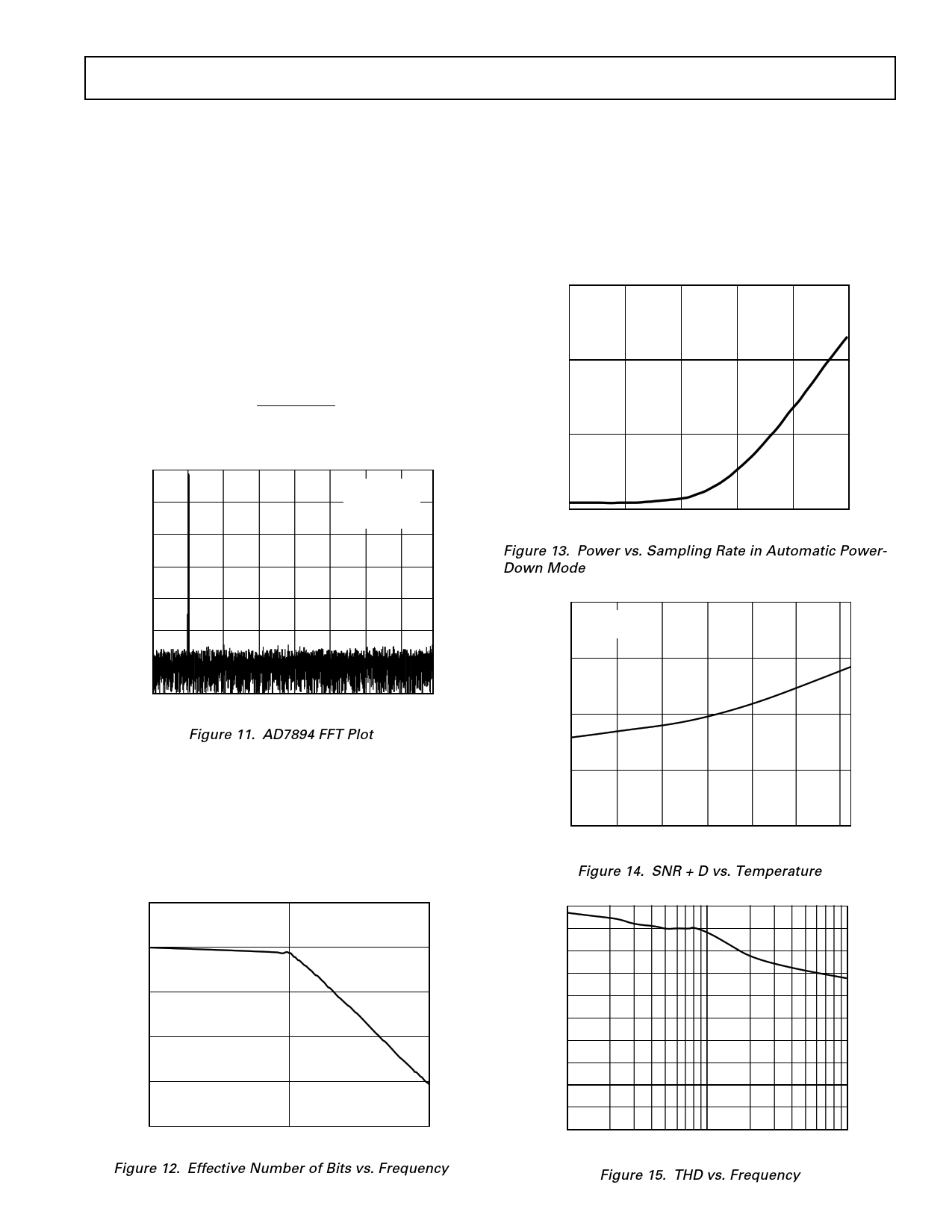

Dynamic Performance (Mode 1 Only)

With a conversion time of 5 µs, the AD7894 is ideal for wide

bandwidth signal processing applications. These applications

require information on the ADC’s effect on the spectral con-

tent of the input signal. Signal to (Noise + Distortion), Total

Harmonic Distortion, Peak Harmonic or Spurious Noise and

Intermodulation Distortion are all specified. Figure 11 shows a

typical FFT plot of a 10 kHz, ± 10␣ V input after being digitized

by the AD7894-10 operating at a 160 kHz sampling rate. The

signal to (noise + distortion) ratio is 80.24 dB and the total

harmonic distortion is –96.35 dB.

The formula for signal to (noise + distortion) ratio (see Ter-

minology section) is related to the resolution or number of bits

in the converter. Rewriting the formula, below, gives a mea-

sure of performance expressed in effective number of bits (N):

Power Considerations

In the automatic power-down mode the part may be operated at

a sample rate that is considerably less than 160 kHz. In this

case, the power consumption will be reduced and will depend

on the sample rate. Figure 13 shows a graph of the power con-

sumption versus sampling rates from 1 Hz to 100 kHz in the

automatic power-down mode. The conditions are 5 V supply

+25°C. The SCLK pin was held low and no data was read from

the part.

100

10

N = (SNR –1.76)

6.02

where SNR is Signal to (Noise + Distortion) Ratio.

1

0

fS = 160kHz

–20

FIN = 10kHz

SNR = 80.24dB

0.1

THD = –96.35dB

1

10

100

1000

10000 100000

–40 SAMPLING FREQUENCY – Hz

Figure 13. Power vs. Sampling Rate in Automatic Power-

–60 Down Mode

–80

–100

–120

82

fS = 160kHz

FIN = 10kHz

81

–140

0

10 20 30 40 50 60

FREQUENCY – kHz

Figure 11. AD7894 FFT Plot

70

80

The effective number of bits for a device can be calculated from

its measured signal to (noise + distortion) ratio. Figure 12

shows a typical plot of effective number of bits versus frequency

for the AD7894 from dc to fSAMPLING/2. The sampling fre-

quency is 160 kHz. The plot shows that the AD7894 converts

an input sine wave of 10␣ kHz to an effective numbers of bits of

13.00, which equates to a signal to (noise + distortion) level of

80.02 dB.

14

13

12

11

10

9

10 100 1000

FREQUENCY – kHz

Figure 12. Effective Number of Bits vs. Frequency

REV. 0

–11–

80

79

78

–40

–20

0

20 40 60 80

TEMPERATURE – ؇C

Figure 14. SNR + D vs. Temperature

100

90

80

70

60

50

40

30

20

10

0

10

100

FREQUENCY – kHz

Figure 15. THD vs. Frequency

1000

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet AD7894.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD7890 | 12-Bit Serial Data Acquisition System | Analog Devices |

| AD7891 | 12-Bit High Speed Data Acquisition System | Analog Devices |

| AD7892 | LC2MOS Single Supply/ 12-Bit 600 kSPS ADC | Analog Devices |

| AD7893 | LC2MOS 12-Bit/ Serial 6 us ADC in 8-Pin Package | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |