|

|

PDF AD768 Data sheet ( Hoja de datos )

| Número de pieza | AD768 | |

| Descripción | 16-Bit/ 30 MSPS D/A Converter | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD768 (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

a

FEATURES

30 MSPS Update Rate

16-Bit Resolution

Linearity: 1/2 LSB DNL @ 14 Bits

1 LSB INL @ 14 Bits

Fast Settling: 25 ns Full-Scale Settling to 0.025%

SFDR @ 1 MHz Output: 86 dBc

THD @ 1 MHz Output: 71 dBc

Low Glitch Impulse: 35 pV-s

Power Dissipation: 465 mW

On-Chip 2.5 V Reference

Edge-Triggered Latches

Multiplying Reference Capability

APPLICATIONS

Arbitrary Waveform Generation

Communications Waveform Reconstruction

Vector Stroke Display

16-Bit, 30 MSPS

D/A Converter

AD768

(MSB)

DB15

DB0

(LSB)

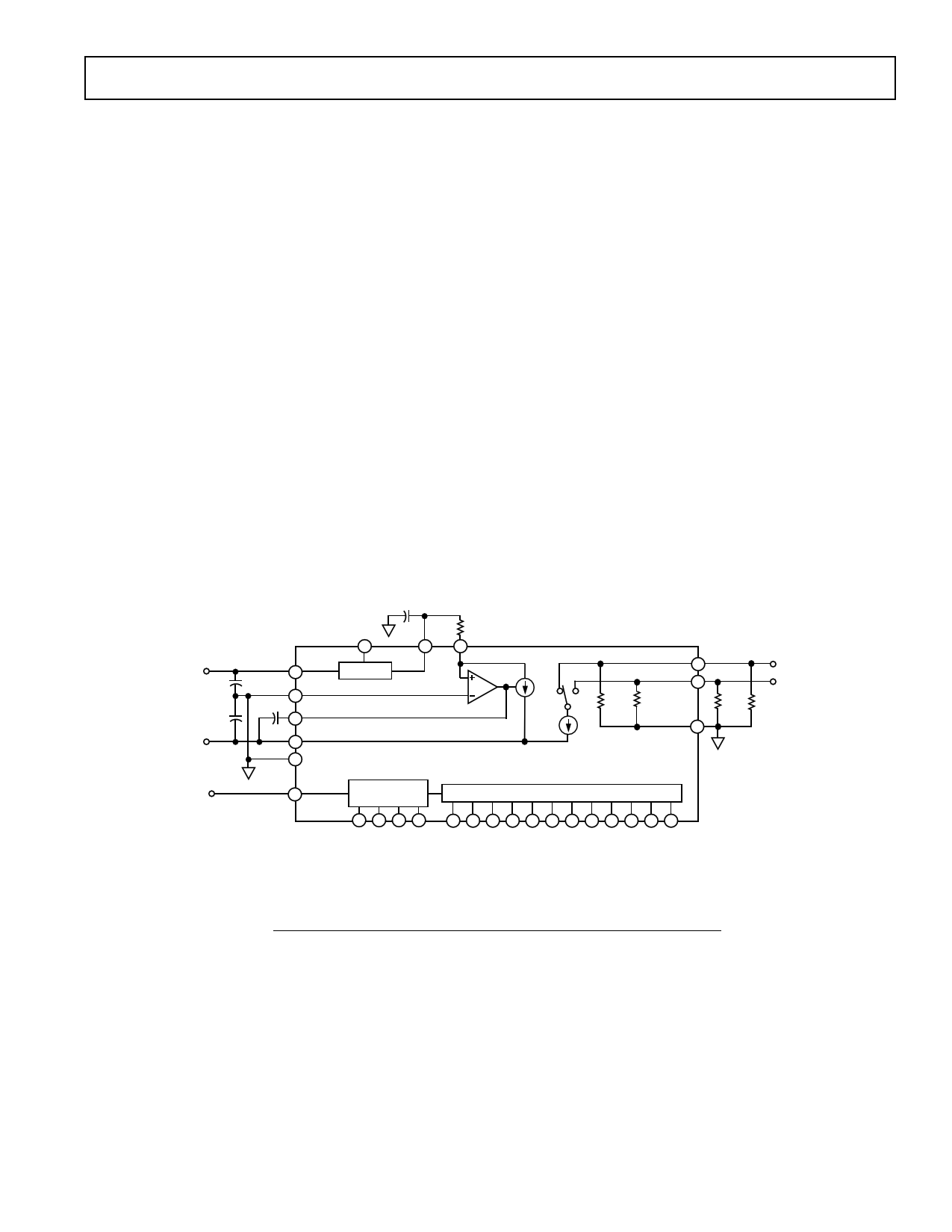

FUNCTIONAL BLOCK DIAGRAM

DCOM

VDD

AD768

MSB

DECODER

AND

EDGE-

TRIGGERED

BIT

LATCHES

MSBs: SEGMENTED

CURRENT SOURCES

AND SWITCHES

LSBs:

CURRENT SOURCES,

SWITCHES, AND

1kΩ R-2R

LADDERS

1k

1k

2.5V

BANDGAP

REFERENCE

CONTROL

AMP

CLOCK NC REFCOM REFOUT IREFIN NR

IOUTA

IOUTB

LADCOM

VEE

PRODUCT DESCRIPTION

The AD768 is a 16-bit, high speed digital-to-analog converter

(DAC) that offers exceptional ac and dc performance. The

AD768 is manufactured on ADI’s Advanced Bipolar CMOS

(ABCMOS) process, combining the speed of bipolar transistors,

the accuracy of laser-trimmable thin film resistors, and the effi-

ciency of CMOS logic. A segmented current source architecture

is combined with a proprietary switching technique to reduce

glitch energy and maximize dynamic accuracy. Edge triggered

input latches and a temperature compensated bandgap reference

have been integrated to provide a complete monolithic DAC

solution.

The AD768 is a current-output DAC with a nominal full-scale

output current of 20 mA and a 1 kΩ output impedance. Differ-

ential current outputs are provided to support single-ended

or differential applications. The current outputs may be tied

directly to an output resistor to provide a voltage output, or fed

to the summing junction of a high speed amplifier to provide a

buffered voltage output. Also, the differential outputs may be

interfaced to a transformer or differential amplifier.

The on-chip reference and control amplifier are configured for

maximum accuracy and flexibility. The AD768 can be driven by

the on-chip reference or by a variety of external reference volt-

ages based on the selection of an external resistor. An external

capacitor allows the user to optimally trade off reference band-

width and noise performance.

The AD768 operates on ± 5 V supplies, typically consuming

465 mW of power. The AD768 is available in a 28-pin SOIC

package and is specified for operation over the industrial tem-

perature range.

PRODUCT HIGHLIGHTS

1. The low glitch and fast settling time provide outstanding

dynamic performance for waveform reconstruction or digital

synthesis requirements, including communications.

2. The excellent dc accuracy of the AD768 makes it suitable for

high speed A/D conversion applications.

3. On-chip, edge-triggered input CMOS latches interface

readily to CMOS logic families. The AD768 can support up-

date rates up to 40 MSPS.

4. A temperature compensated, 2.5 V bandgap reference is

included on-chip allowing for generation of the reference

input current with the use of a single external resistor. An ex-

ternal reference may also be used.

5. The current output(s) of the AD768 may be used singly or

differentially, either into a load resistor, external op amp

summing junction or transformer.

6. Proper selection of an external resistor and compensation

capacitor allow the performance-conscious user to optimize

the AD768 reference level and bandwidth for the target

application.

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

© Analog Devices, Inc., 1996

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700

Fax: 617/326-8703

1 page

AD768

DEFINITIONS OF SPECIFICATIONS

Linearity Error (Also Called Integral Nonlinearity or INL)

Linearity error is defined as the maximum deviation of the ac-

tual analog output from the ideal output, determined by a

straight line drawn from zero to full scale.

Differential Nonlinearity (or DNL)

DNL is the measure of the variation in analog value, normalized

to full scale, associated with a 1 LSB change in digital input code.

Monotonicity

A D/A converter is monotonic if the output either increases or

remains constant as the digital input increases.

Offset Error

The deviation of the output current from the ideal of zero is

called offset error. For IOUTA, 0 mA output is expected when

the inputs are all 0s. For IOUTB, 0 mA output is expected

when all inputs are set to 1s.

Gain Error

The difference between the actual and ideal output span. The

actual span is determined by the output when all inputs are set

to 1s minus the output when all inputs are set to 0s. The ideal

output current span is 4× the current applied to the IREFIN pin.

Output Compliance Range

The range of allowable voltage at the output of a current-output

DAC. Operation beyond the maximum compliance limits may

cause either output stage saturation or breakdown, resulting in

nonlinear performance.

Temperature Drift

Temperature drift is specified as the maximum change from the

ambient (+25°C) value to the value at either TMIN or TMAX. For

offset and gain drift, the drift is reported in ppm of full-scale

range (FSR) per degree C. For reference drift, the drift is re-

ported in ppm per degree C.

Power Supply Rejection

The maximum change in the full-scale output as the supplies

are varied from nominal to minimum and maximum specified

voltages.

Settling Time

The time required for the output to reach and remain within a

specified error band about its final value, measured from the

start of the output transition.

Spurious-Free Dynamic Range

The difference, in dB, between the rms amplitude of the

input signal and the peak spurious signal over the specified

bandwidth.

Total Harmonic Distortion

THD is the ratio of the rms sum of the first six harmonic com-

ponents to the rms value of the measured input signal. It is ex-

pressed as a percentage or in decibels (dB).

Glitch Impulse

Asymmetrical switching times in a DAC give rise to undesired

output transients which are quantified by a glitch impulse. It is

specified as the net area of the glitch in pV-sec.

+5V

1µF

1µF

–5V

CLOCK

CREFCOMP

VDD

25

1µF

43

NC REFOUT

+2.5V REF

1µF

CNR

REFCOM

5

NR

2

VEE

26

15 DCOM

AD768

CLOCK

16

MSB DECODE

& LATCHES

RREF

500Ω

6

REFIN

5mA

RLAD

1kΩ

IOUTA

1

IOUTB

27

RLAD

1kΩ

LADCOM

28

IOUTA

IOUTB

50Ω

RLOAD

50Ω

SEGMENTED

CURRENT

SOURCES

CURRENT SOURCES

AND R-2R LADDER

LATCHES – LOWER 12 BITS

24 23 22 21

20 19 18 17 14 13 12 11 10 9 8 7

Figure 1. Functional Block Diagram and Basic Hookup

FUNCTIONAL DESCRIPTION

The AD768 is a current-output DAC with a nominal full-scale

current of 20 mA and a 1 kΩ output impedance. Differential

outputs are provided to support single-ended or differential

applications. The DAC architecture combines segmented cur-

rent sources for the top four bits (MSBs) and a 1 kΩ R-2R lad-

der for the lower 12 bits (LSBs). The DAC current sources are

implemented with laser-trimmable thin film resistors for excel-

lent dc linearity. A proprietary switching technique is utilized to

reduce glitch energy and maximize dynamic accuracy.

The digital interface offers CMOS compatible edge-triggered

input latches that interface readily to CMOS logic and supports

clock rates up to 40 MSPS. A temperature compensated 2.5 V

bandgap reference is integrated on-chip to drive the AD768 ref-

erence input current with the use of a single external resistor.

The functional block diagram in Figure 1 is a simple representa-

tion of the internal circuitry to aid the understanding of the

AD768’s operation. The DAC transfer function is described,

and followed by a detailed description of each key portion of the

circuit. Typical circuit configurations are shown in the section

APPLYING THE AD768.

REV. B

–5–

5 Page

AD768

For the values given in Figure 24, I3 equals 4 mA, which results

in a nominal unipolar output swing of 0 V to 2 V. Note, since

A1 has an inverting gain of approximately –4 and a noise gain of

+5, A1’s distortion and noise performance should be considered.

AD768

IOUTA 1

IOUTB 27

LADCOM 28

I1

I2

RP

20Ω

I3

RFF

100Ω

RL

24.9Ω

RFB

500Ω

A1

Figure 24. 0 V to 2 V Buffered Unipolar Output Using a

Current Divider

Bipolar Configuration

Bipolar mode is accomplished by providing an offset current,

IBIPOLAR, to the I/V amplifier’s (A1) summing junction. By set-

ting IBIPOLAR to exactly half the full-scale current flowing

through RFB, the resulting output voltage will be symmetrical

about the summing junction voltage, typically ground. Figure 25

shows the implementation for a bipolar ± 2.5 V buffered voltage

output. The resistor divider sets the full-scale current for IDAC to

5 mA. The internal 2.5 V reference generates a 2.5 mA IBIPOLAR

current across RBIP. An output voltage of 0 V is produced when

the DAC is set to half scale (100. . .0) such that the 2.5 mA cur-

rent, IDAC, is exactly offset by IBIPOLAR. As the DAC is varied

from zero to full-scale, the output voltage swings from –2.5 V to

+2.5 V. Note, in configurations that require more than 15 mA

of total current from REFOUT, an external buffer is required.

Op amps such as the AD811, AD8001, and AD9631 are good

selections for superior dynamic performance. In dc applications,

op amps such as the AD845 or AD797 may be more appropriate.

AD768

REFOUT 3

IOUTA 1

IOUTB 27

LADCOM 28

RBIP

1kΩ

C IBIPOLAR

75Ω IDAC

24.9Ω

RP

20Ω

RFB

1kΩ

A1

Figure 25. Bipolar ±2.5 V Buffered Voltage Output

DIFFERENTIAL OUTPUT CONFIGURATIONS

AC Coupling via a Transformer

Applications that do not require baseband operation typically

use transformer coupling. Transformer coupling the comple-

mentary outputs of the AD768 to a load has the inherent benefit

of providing electrical isolation while consuming no additional

power. Also, a properly applied transformer should not degrade

the AD768’s output signal with respect to noise and distortion,

since the transformer is a passive device. Figure 26 shows a

center-tapped output transformer that provides the necessary dc

load conditions at the outputs IOUTA and IOUTB to drive a

± 0.5 V signal into a 50 Ω load. In this particular circuit, the cen-

ter-tapped transformer has an impedance ratio of 4 that corre-

sponds to a turns ratio of 2. Hence, any load, RL, referred to the

primary side is multiplied by a factor of 4 (i.e., in this case

200 Ω). To avoid dc current from flowing into the R-2R ladder

of the DAC, the center tap of the transformer should be con-

nected to LADCOM.

In order to comply with the minimum voltage compliance of

–1.2 V, the maximum differential resistance seen between

IOUTA and IOUTB should not exceed 240 Ω. Note that the

differential resistance consists of the load RL, referred to the

primary side of the transformer in parallel with any added differ-

ential resistance, RDIFF, across the two outputs. RDIFF is typically

added to the primary side of the transformer to match the effec-

tive primary source impedance to the load (i.e., in this case

200 Ω).

AD768

IOUTA 1

IOUTB 27

LADCOM 28

RDIFF

200Ω

T1 RL

50Ω

4:1 IMPEDANCE

RATIO

T1 = MINI-CIRCUITS T4-6T

Figure 26. Differential Output Using a Transformer

DC COUPLING VIA AN AMPLIFIER

A dc differential to single-ended conversion can be easily ac-

complished using the circuit shown in Figure 27. This circuit

will attenuate both ac and dc common-mode error sources due

to the differential nature of the circuit. Thus, common-mode

noise (i.e., clock feedthrough) as well as dc unipolar offset errors

will be significantly reduced. Also, excellent temperature stabil-

ity can be obtained by using temperature tracking, thin film

resistors for R and RREF. The design equations for the circuit are

provided such that the voltage output swing and IREF can be

optimized for a given application.

AD768

R*

IOUTA 1

IOUTB 27

LADCOM 28

R*

REFIN 6

REFOUT 3

RREF*

A1

IREF

VOUT

VOUT = ±4 IREF R

WHERE

IREF

=

2.5V

RREF

VOUT ± 2V

R = 200Ω

RREF = 5 x 200Ω

*OHMTEK TDP-1403

Figure 27. DC Differential to Single-Ended Conversion

POWER AND GROUNDING CONSIDERATIONS

In systems seeking to simultaneously achieve high speed and

high accuracy, the implementation and construction of the

printed circuit board design is often as important as the circuit

design. Proper RF techniques must be used in device selection,

placement and routing, and supply bypassing and grounding.

Maintaining low noise on power supplies and ground is critical

to obtaining optimum results from the AD768. Figure 28 pro-

vides an illustration of the recommended printed circuit board

ground plane layout which is implemented on the AD768 evalu-

ation board.

REV. B

–11–

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet AD768.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD760 | 16/18-Bit Self-Calibrating Serial/Byte DACPORT | Analog Devices |

| AD7605-4 | Simultaneous Sampling ADC | Analog Devices |

| AD7606 | 8-/6-/4-Channel DAS | Analog Devices |

| AD7606-4 | 8-/6-/4-Channel DAS | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |