|

|

PDF AD9753 Data sheet ( Hoja de datos )

| Número de pieza | AD9753 | |

| Descripción | 12-Bit 300 MSPS High-Speed TxDAC+ D/A Converter | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD9753 (archivo pdf) en la parte inferior de esta página. Total 29 Páginas | ||

|

No Preview Available !

FEATURES

12-Bit Dual Muxed Port DAC

300 MSPS Output Update Rate

Excellent SFDR and IMD Performance

SFDR to Nyquist @ 25 MHz Output: 69 dB

Internal Clock Doubling PLL

Differential or Single-Ended Clock Input

On-Chip 1.2 V Reference

Single 3.3 V Supply Operation

Power Dissipation: 155 mW @ 3.3 V

48-Lead LQFP

APPLICATIONS

Communications: LMDS, LMCS, MMDS

Base Stations

Digital Synthesis

QAM and OFDM

12-Bit, 300 MSPS

High Speed TxDAC+®D/A Converter

AD9753*

FUNCTIONAL BLOCK DIAGRAM

DVDD DCOM

AVDD ACOM

PORT1

LATCH

PORT2

LATCH

MUX

DAC

IOUTA

IOUTB

CLK+

CLK–

CLKVDD

PLLVDD

CLKCOM

PLL

CLOCK

MULTIPLIER

REFERENCE

AD9753

RESET LPF DIV0 DIV1 PLLLOCK

REFIO

FSADJ

GENERAL DESCRIPTION

The AD9753 is a dual, muxed port, ultrahigh speed, single-

channel, 12-bit CMOS DAC. It integrates a high quality 12-bit

TxDAC+ core, a voltage reference, and digital interface circuitry

into a small 48-lead LQFP package. The AD9753 offers excep-

tional ac and dc performance while supporting update rates up

to 300 MSPS.

The AD9753 has been optimized for ultrahigh speed applica-

tions up to 300 MSPS where data rates exceed those possible on

a single data interface port DAC. The digital interface consists

of two buffered latches as well as control logic. These latches

can be time multiplexed to the high speed DAC in several ways.

This PLL drives the DAC latch at twice the speed of the exter-

nally applied clock and is able to interleave the data from the

two input channels. The resulting output data rate is twice that

of the two input channels. With the PLL disabled, an external

2× clock may be supplied and divided by two internally.

The CLK inputs (CLK+/CLK–) can be driven either differen-

tially or single-ended, with a signal swing as low as 1 V p-p.

The DAC utilizes a segmented current source architecture

combined with a proprietary switching technique to reduce

glitch energy and to maximize dynamic accuracy. Differential

current outputs support single-ended or differential applica-

tions. The differential outputs each provide a nominal full-scale

current from 2 mA to 20 mA.

The AD9753 is manufactured on an advanced low cost 0.35 µm

CMOS process. It operates from a single supply of 3.0 V to 3.6 V

and consumes 155 mW of power.

PRODUCT HIGHLIGHTS

1. The AD9753 is a member of a pin compatible family of high

speed TxDAC+s providing 10-, 12-, and 14-bit resolution.

2. Ultrahigh Speed 300 MSPS Conversion Rate.

3. Dual 12-Bit Latched, Multiplexed Input Ports. The AD9753

features a flexible digital interface allowing high speed data

conversion through either a single or dual port input.

4. Low Power. Complete CMOS DAC function operates on

155 mW from a 3.0 V to 3.6 V single supply. The DAC full-

scale current can be reduced for lower power operation.

5. On-Chip Voltage Reference. The AD9753 includes a 1.20 V

temperature-compensated band gap voltage reference.

*Protected by U.S. Patent numbers 5450084, 5568145, 5689257, and

5703519.

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

1 page

AD9753

DIGITAL SPECIFICATIONS (TMIN to TMAX, AVDD = DVDD = PLLVDD = CLKVDD = 3.3 V, IOUTFS = 20 mA, unless otherwise noted.)

Parameter

Min

Typ

Max

Unit

DIGITAL INPUTS

Logic 1

2.1 3

V

Logic 0

0 0.9 V

Logic 1 Current

–10 +10 µA

Logic 0 Current

–10 +10 µA

Input Capacitance

5 pF

Input Setup Time (tS), TA = 25°C

1.0 0.5

Input Hold Time (tH), TA = 25°C

1.0 0.5

Latch Pulsewidth (tLPW), TA = 25°C

1.5

Input Setup Time (tS, PLLVDD = 0 V), TA = 25°C

–1.0 –1.5

Input Hold Time (tH, PLLVDD = 0 V), TA = 25°C

2.5 1.7

CLK to PLLLOCK Delay (tD, PLLVDD = 0 V), TA = 25°C

3.5

4.0

Latch Pulsewidth (tLPW PLLVDD = 0 V), TA = 25°C

1.5

PLLOCK (VOH)

3.0

PLLOCK (VOL)

0.3

ns

ns

ns

ns

ns

ns

ns

V

V

CLK INPUTS

Input Voltage Range

Common-Mode Voltage

Differential Voltage

Min CLK Frequency*

0 3V

0.75 1.5

2.25 V

0.5 1.5

V

6.25 MHz

*Min CLK Frequency applies only when using internal PLL. When PLL is disabled, there is no minimum CLK frequency.

Specifications subject to change without notice.

–4– REV. B

5 Page

AD9753

0.1F

RSET

2k⍀

3.0V TO 3.6V

1.2V REF

REFIO

DVDD AVDD

PMOS CURRENT

SOURCE ARRAY

FSADJ

SEGMENTED

SWITCHES FOR

DB0 TO DB11

DAC

DAC LATCH

AD9753

DCOM

ACOM

2 –1 MUX

PORT 1 LATCH

PORT 2 LATCH

DB0 – DB11

DB0 – DB11

DIGITAL DATA INPUTS

PLL

CIRCUITRY

VDIFF = VOUTA – VOUTB

IOUTA

IOUTB

PLLVDD

CLKVDD

CLK+

CLK–

CLKCOM

RESET

LPF

VOUT B

RLOAD

50⍀

VOUT A

RLOAD

50⍀

DIV0 DIV1 PLLLOCK

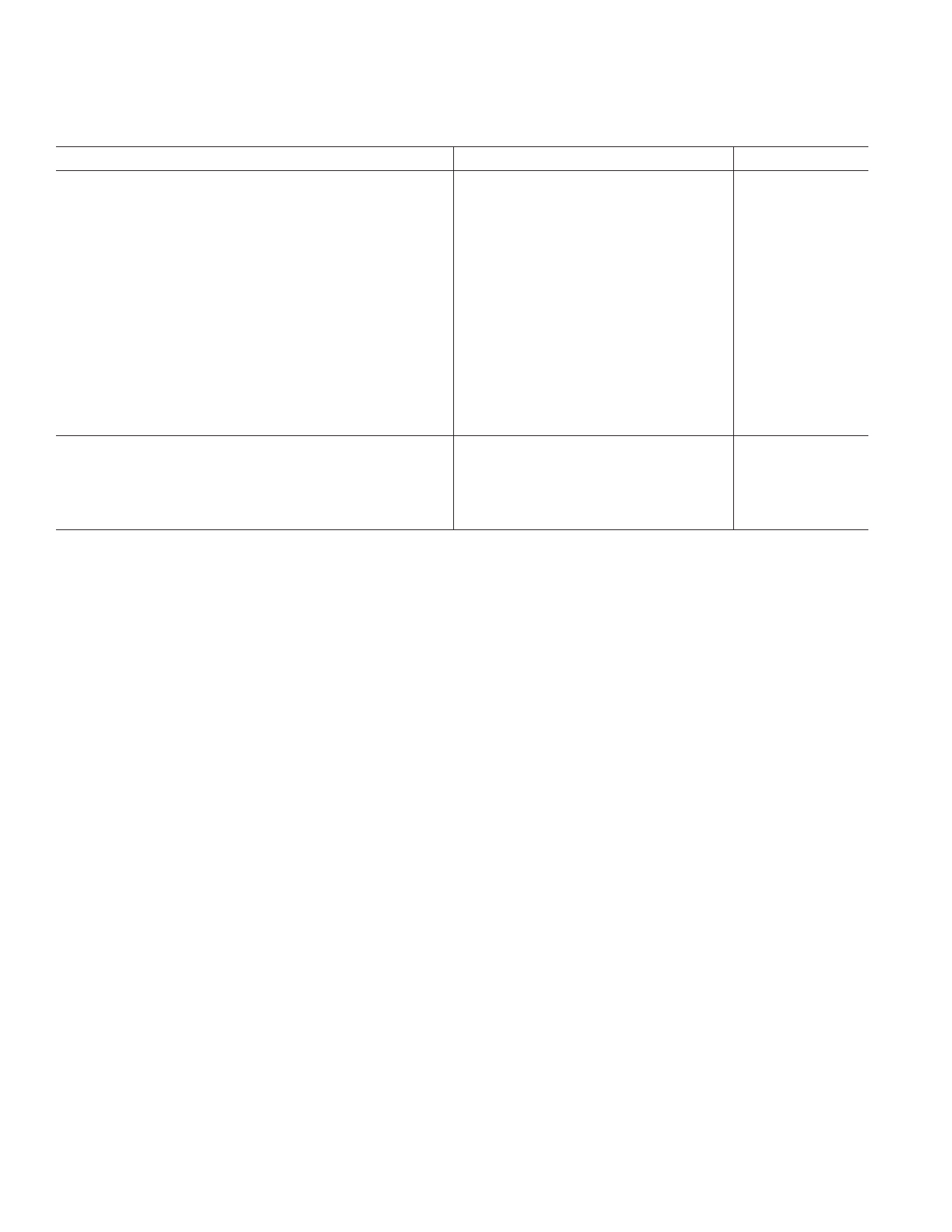

Figure 3. Simplified Block Diagram

FUNCTIONAL DESCRIPTION

Figure 3 shows a simplified block diagram of the AD9753. The

AD9753 consists of a PMOS current source array capable of

providing up to 20 mA of full-scale current, IOUTFS. The

array is divided into 31 equal sources that make up the five

most significant bits (MSBs). The next four bits, or middle bits,

consist of 15 equal current sources whose value is 1/16th of an

MSB current source. The remaining LSBs are a binary weighted

fraction of the middle bit current sources. Implementing the

middle and lower bits with current sources, instead of an R-2R

ladder, enhances dynamic performance for multitone or low

amplitude signals and helps maintain the DAC’s high output

impedance (i.e., >100 kΩ).

All of the current sources are switched to one of the two

outputs (i.e., IOUTA or IOUTB) via PMOS differential current

switches. The switches are based on a new architecture that

drastically improves distortion performance. This new switch

architecture reduces various timing errors and provides matching

complementary drive signals to the inputs of the differential

current switches.

The analog and digital sections of the AD9753 have separate

power supply inputs (i.e., AVDD and DVDD) that can operate

independently over a 3.0 V to 3.6 V range. The digital section,

which is capable of operating at a 300 MSPS clock rate, consists

of edge-triggered latches and segment decoding logic circuitry.

The analog section includes the PMOS current sources, the

associated differential switches, a 1.20 V band gap voltage refer-

ence, and a reference control amplifier.

The full-scale output current is regulated by the reference control

amplifier and can be set from 2 mA to 20 mA via an external

resistor, RSET. The external resistor, in combination with both

the reference control amplifier and voltage reference VREFIO, sets

the reference current IREF, which is replicated to the segmented

current sources with the proper scaling factor. The full-scale

current, IOUTFS, is 32 times the value of IREF.

REFERENCE OPERATION

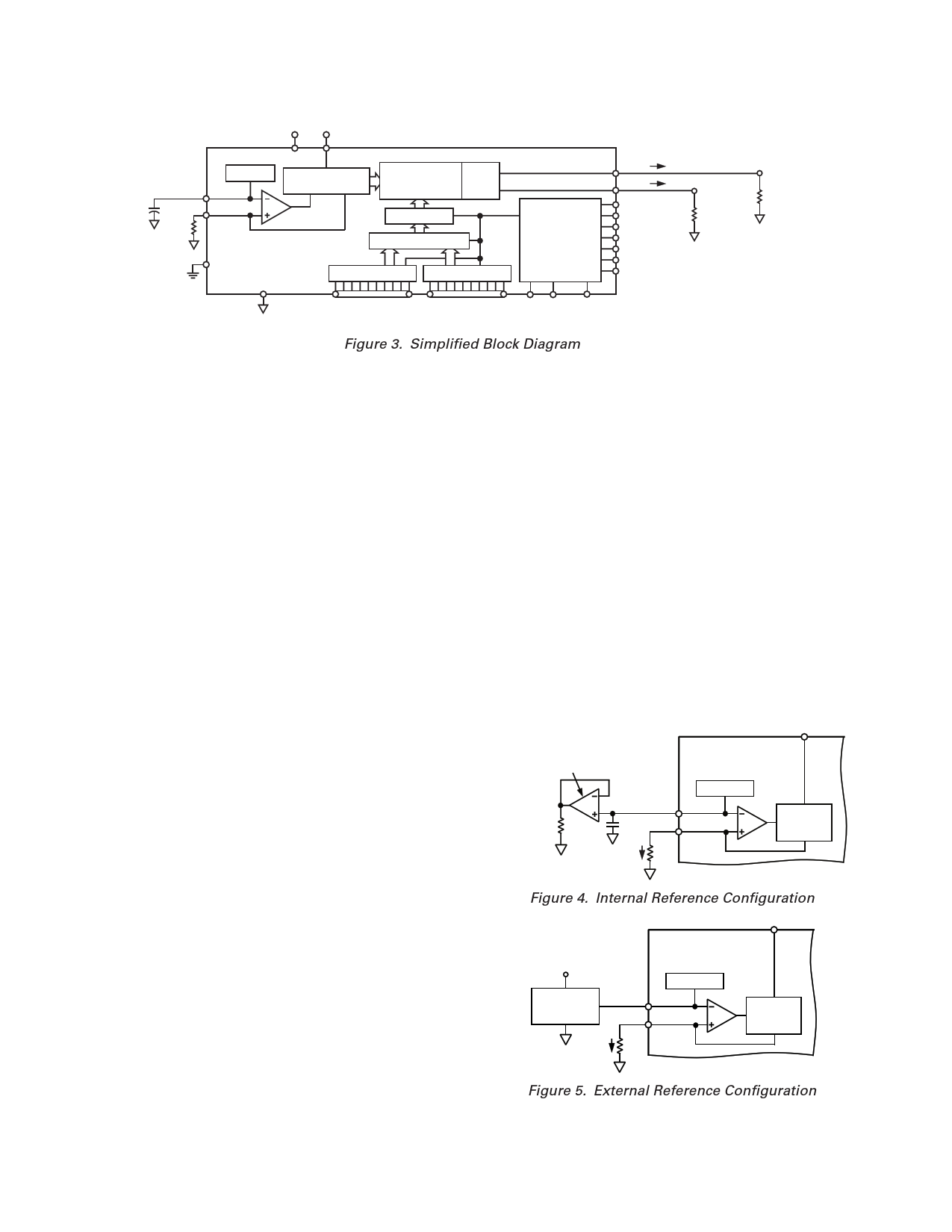

The AD9753 contains an internal 1.20 V band gap reference.

This can easily be overdriven by an external reference with no

effect on performance. REFIO serves as either an input or output,

depending on whether the internal or an external reference is

used. To use the internal reference, simply decouple the REFIO

pin to ACOM with a 0.1 µF capacitor. The internal reference

voltage will be present at REFIO. If the voltage at REFIO is to

be used elsewhere in the circuit, an external buffer amplifier

with an input bias current less than 100 nA should be used. An

example of the use of the internal reference is given in Figure 4.

A low impedance external reference can be applied to REFIO,

as shown in Figure 5. The external reference may provide either

a fixed reference voltage to enhance accuracy and drift perfor-

mance or a varying reference voltage for gain control. Note

that the 0.1 µF compensation capacitor is not required since

the internal reference is overdriven, and the relatively high input

impedance of REFIO minimizes any loading of the external

reference.

OPTIONAL

EXTERNAL

REFERENCE

BUFFER

ADDITIONAL

EXTERNAL

LOAD

AD9753

REFERENCE

SECTION

AVDD

0.1F

1.2V REF

REFIO

FSADJ

CURRENT

SOURCE

ARRAY

IREF 2k⍀

Figure 4. Internal Reference Configuration

AVDD

EXTERNAL

REFERENCE

IREF

AD9753

REFERENCE

SECTION

AVDD

1.2V REF

REFIO

FSADJ

CURRENT

SOURCE

ARRAY

2k⍀

Figure 5. External Reference Configuration

–10–

REV. B

11 Page | ||

| Páginas | Total 29 Páginas | |

| PDF Descargar | [ Datasheet AD9753.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD9750 | 10-Bit/ 125 MSPS High Performance TxDAC D/A Converter | Analog Devices |

| AD9751 | 10-Bit 300 MSPS High-Speed TxDAC+ D/A Converter | Analog Devices |

| AD9752 | 12-Bit/ 125 MSPS High Performance TxDAC D/A Converter | Analog Devices |

| AD9753 | 12-Bit 300 MSPS High-Speed TxDAC+ D/A Converter | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |