|

|

PDF AD8325 Data sheet ( Hoja de datos )

| Número de pieza | AD8325 | |

| Descripción | 5 V CATV Line Driver Fine Step Output Power Control | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD8325 (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

a

FEATURES

Supports DOCSIS Standard for Reverse Path

Transmission

Gain Programmable in 0.75 dB Steps Over a 59.45 dB

Range

Low Distortion at 61 dBmV Output

–57 dBc SFDR at 21 MHz

–55 dBc SFDR at 42 MHz

Output Noise Level

–48 dBmV in 160 kHz

Maintains 75 � Output Impedance

Transmit Enable and Transmit Disable Modes

Upper Bandwidth: 100 MHz (Full Gain Range)

5 V Supply Operation

Supports SPI Interfaces

APPLICATIONS

Gain-Programmable Line Driver

DOCSIS High-Speed Data Modems

Interactive Cable Set-Top Boxes

PC Plug-in Cable Modems

General-Purpose Digitally Controlled Variable Gain Block

5 V CATV Line Driver Fine Step

Output Power Control

AD8325

FUNCTIONAL BLOCK DIAGRAM

VCC (7 PINS)

BYP

R1 AD8325

VIN+

VIN–

DIFF OR

SINGLE

INPUT

AMP

VERNIER

R2

ZIN (SINGLE) = 800�

ZIN (DIFF) = 1.6k�

ATTENUATION

CORE

8

DECODE

POWER

AMP

ZOUT DIFF =

75�

VOUT+

VOUT–

8

DATA LATCH

POWER-DOWN

LOGIC

8

SHIFT

REGISTER

DATEN DATA CLK GND (11 PINS) TXEN SLEEP

GENERAL DESCRIPTION

The AD8325 is a low-cost, digitally controlled, variable gain ampli

fier optimized for coaxial line driving applications such as cable

modems that are designed to the MCNS-DOCSIS upstream

standard. An 8-bit serial word determines the desired output gain

over a 59.45 dB range resulting in gain changes of 0.7526 dB/LSB.

The AD8325 comprises a digitally controlled variable attenuator

of 0 dB to –59.45 dB, which is preceded by a low noise, fixed

gain buffer and is followed by a low distortion high power ampli

fier. The AD8325 accepts a differential or single-ended input

signal. The output is specified for driving a 75 W load, such as

coaxial cable.

Distortion performance of –57 dBc is achieved with an output

level up to 61 dBmV at 21 MHz bandwidth. A key performance

and cost advantage of the AD8325 results from the ability to

maintain a constant 75 W output impedance during Transmit

Enable and Transmit Disable conditions. In addition, this

device has a sleep mode function that reduces the quiescent

current to 4 mA.

The AD8325 is packaged in a low-cost 28-lead TSSOP, operates

from a single 5 V supply, and has an operational temperature

range of –40∞C to +85∞C.

–50

VOUT = 62dBmV

@ MAX GAIN

–52

VOUT = 61dBmV

@ MAX GAIN

–54

–56

–58

–60

–62

–64

5

VOUT = 60dBmV

@ MAX GAIN

VOUT = 59dBmV

@ MAX GAIN

15 25 35 45 55

FUNDAMENTAL FREQUENCY – MHz

65

Figure 1. Worst Harmonic Distortion vs. Gain Control

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.analog.com

Fax: 781/461-3113 © 2005 Analog Devices, Inc. All rights reserved.

1 page

AD8325

ABSOLUTE MAXIMUM RATINGS*

Supply Voltage +VS

Pins 5, 9, 10, 19, 20, 23, 27 . . . . . . . . . . . . . . . . . . . . . . 6 V

Input Voltages

Pins 25, 26 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 0.5 V

Pins 1, 2, 3, 6, 7 . . . . . . . . . . . . . . . . . . . . . –0.8 V to +5.5 V

Internal Power Dissipation

TSSOP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.9 W

Operating Temperature Range . . . . . . . . . . . –40∞C to +85∞C

Storage Temperature Range . . . . . . . . . . . . –65∞C to +150∞C

Lead Temperature, Soldering 60 seconds . . . . . . . . . . . 300∞C

*Stresses above those listed under Absolute Maximum Ratings may cause perma

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

ORDERING GUIDE

Model

Temperature Range

AD8325ARU

AD8325ARU-REEL

AD8325ARUZ2

AD8325ARUZ-REEL2

AD8325-EVAL

–40∞C to +85∞C

–40∞C to +85∞C

–40∞C to +85∞C

–40∞C to +85∞C

1Thermal Resistance measured on SEMI standard 4-layer board.

2Z = Pb-free part.

Package Description

28-Lead TSSOP

28-Lead TSSOP

28-Lead TSSOP

28-Lead TSSOP

Evaluation Board

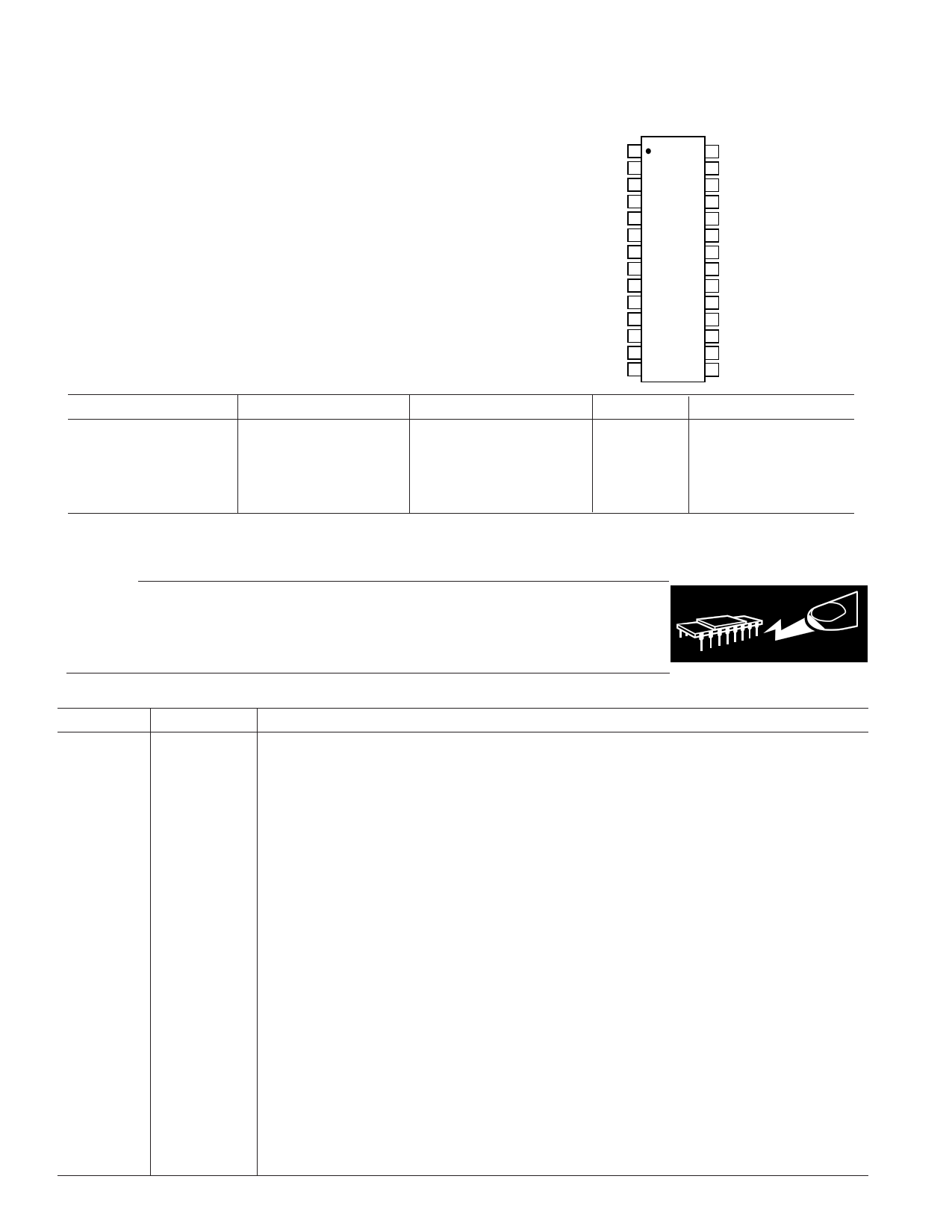

PIN CONFIGURATION

DATEN 1

28 GND

SDATA

CLK

GND

VCC

TXEN

SLEEP

GND

2 27 VCC

3 26 VIN–

4 25 VIN+

5 24 GND

6 AD8325 23 VCC

7 TOP VIEW 22 GND

8 (Not to Scale) 21 BYP

VCC 9

VCC 10

GND 11

20 VCC

19 VCC

18 GND

GND 12

17 GND

GND 13

16 GND

OUT– 14

15 OUT+

�JA

67.7∞C/W1

67.7∞C/W1

67.7∞C/W1

67.7∞C/W1

Package Option

RU-28

RU-28

RU-28

RU-28

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD8325 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

Pin No.

1

Mnemonic

DATEN

2 SDATA

3 CLK

4, 8, 11, 12,

13, 16, 17, 18,

22, 24, 28

5, 9, 10, 19,

20, 23, 27

6

7

GND

VCC

TXEN

SLEEP

14 OUT–

15 OUT+

21 BYP

25 VIN+

26 VIN–

PIN FUNCTION DESCRIPTIONS

Description

Data Enable Low Input. This port controls the 8-bit parallel data latch and shift register. A Logic

0-to-1 transition transfers the latched data to the attenuator core (updates the gain) and simulta

neously inhibits serial data transfer into the register. A 1-to-0 transition inhibits the data latch

(holds the previous gain state) and simultaneously enables the register for serial data load.

Serial Data Input. This digital input allows for an 8-bit serial (gain) word to be loaded into the

internal register with the MSB (Most Significant Bit) first.

Clock Input. The clock port controls the serial attenuator data transfer rate to the 8-bit master-

slave register. A Logic 0-to-1 transition latches the data bit and a 1-to-0 transfers the data bit to

the slave. This requires the input serial data word to be valid at or before this clock transition.

Common External Ground Reference.

Common Positive External Supply Voltage. A 0.1 mF capacitor must decouple each pin.

Logic “0” disables transmission. Logic “1” enables transmission.

Low Power Sleep Mode. Logic 0 enables Sleep mode, where ZOUT goes to 400 W and supply

current is reduced to 4 mA. Logic 1 enables normal operation.

Negative Output Signal.

Positive Output Signal.

Internal Bypass. This pin must be externally ac-coupled (0.1 mF cap).

Noninverting Input. DC-biased to approximately VCC/2. Should be ac-coupled with a 0.1 mF

capacitor.

Inverting Input. DC-biased to approximately VCC/2. Should be ac-coupled with a 0.1 mF capacitor.

–4– REV. A

5 Page

AD8325

Differential Inputs

The AD8325-EVAL evaluation board may be driven with a

differential signal in one of two ways. A transformer may be

used to convert a single-ended signal to differential, or a differ

ential signal source may be used. Figure 7 and the following

paragraphs describe each of these methods.

Single-Ended-to-Differential Input (Figure 7, Option 1)

A TOKO 617DB-A0070 1:1 transformer is preinstalled in the

T3 location of the evaluation board. Install 0 W chip resistors at

R14, R15, and R20, and leave R16 through R19 open. For

50 W differential input impedance, install a 51.1 W resistor at R13.

For 75 W differential input impedance, use a 78.7 W resistor.

In this configuration, the input signal must be applied to the

VIN+ port of the evaluation board. For input impedances other

than 50 W or 75 W, the correct value for R13 can be calculated

using the following equation.

Desired Input Impedance = (R13ʈ1600)

Differential Input (Figure 7, Option 2)

If a differential signal source is available, it may be applied

directly to both the VIN+ and VIN– input ports of the evaluation

board. In this case, 0 W chip resistors should be installed at

locations R16 through R19, and R14, R15, and R20 should be

left open. The equation at the end of the preceding paragraph

can be used to compute the correct value for R13 for any

desired differential input impedance. For differential input

impedances of 75 W or 150 W, the value of R13 will be 78.7 W or

165 W respectively.

DIFF IN

T1 R13 AD8325

DIFFERENTIAL INPUT, OPTION 1

VIN+

VIN–

R13 AD8325

DIFFERENTIAL INPUT, OPTION 2

Figure 7. Differential Input Termination Options

Installing the Visual Basic Control Software

To install the “CABDRIVE_25” evaluation board control soft

ware, close all Windows applications and then run “SETUP.EXE”

located on Disk 1 of the AD8325 Evaluation Software. Follow

the on-screen instructions and insert Disk 2 when prompted to

do so. Enter the path of the directory into which the software

will be installed and select the button in the upper left corner to

complete the installation.

Running the Software

To invoke the control software, go to START -> PROGRAMS

-> CABDRIVE_25, or select the AD8325.EXE icon from the

directory containing the software.

Controlling the Gain/Attenuation of the AD8325

The slide bar controls the AD8325’s gain/attenuation, which is

displayed in dB and in V/V. The gain scales at 0.7526 dB per

LSB with the valid codes being from decimal 0 to 79. The gain

code (i.e., position of the slide bar) is displayed in decimal, binary,

and hexadecimal (see Figure 8).

Transmit Enable, Transmit Disable, and Sleep

The “Transmit Enable” and “Transmit Disable” buttons select

the mode of operation of the AD8325 by controlling the logic

level on the asynchronous TXEN pin. The “Transmit Enable”

button applies a Logic 1 to the TXEN pin putting the AD8325

in forward transmit mode. The “Transmit Disable” button

applies a Logic 0 to the TXEN pin selecting reverse mode, where

the forward signal transmission is disabled while a back termina

tion of 75 W is maintained. On early revisions of the software,

the “Transmit Enable” and “Transmit Disable” buttons may be

called “Power-Up” and “Power-Down” respectively. Checking

the “Enable SLEEP Mode” box applies a Logic 0 to the asyn

chronous SLEEP pin, putting the AD8325 into SLEEP mode.

Memory Section

The “MEMORY” section of the software provides a convenient

way to alternate between two gain settings. The “X->M1” but

ton stores the current value of the gain slide bar into memory

while the “RM1” button recalls the stored value, returning the

gain slide bar to that level. The “X->M2” and “RM2” buttons

work in the same manner.

–10–

REV. A

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet AD8325.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD8320 | Serial Digital Controlled Variable Gain Line Driver | Analog Devices |

| AD8321 | Gain Programmable CATV Line Driver | Analog Devices |

| AD8322 | 5 V CATV Line Driver Coarse Step Output Power Control | Analog Devices |

| AD8323 | 5 V CATV Line Driver Fine Step Output Power Control | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |