|

|

PDF ADSP-2188NKST-320 Data sheet ( Hoja de datos )

| Número de pieza | ADSP-2188NKST-320 | |

| Descripción | DSP Microcomputer | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADSP-2188NKST-320 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

a

DSP Microcomputer

ADSP-218xN Series

PERFORMANCE FEATURES

12.5 ns Instruction Cycle Time @1.8 V (Internal), 80 MIPS

Sustained Performance

Single-Cycle Instruction Execution

Single-Cycle Context Switch

3-Bus Architecture Allows Dual Operand Fetches in

Every Instruction Cycle

Multifunction Instructions

Power-Down Mode Featuring Low CMOS Standby

Power Dissipation with 200 CLKIN Cycle Recovery

from Power-Down Condition

Low Power Dissipation in Idle Mode

INTEGRATION FEATURES

ADSP-2100 Family Code Compatible (Easy to Use

Algebraic Syntax), with Instruction Set Extensions

Up to 256K Bytes of On-Chip RAM, Configured as

Up to 48K Words Program Memory RAM

Up to 56K Words Data Memory RAM

Dual-Purpose Program Memory for Both Instruction and

Data Storage

Independent ALU, Multiplier/Accumulator, and Barrel

Shifter Computational Units

Two Independent Data Address Generators

Powerful Program Sequencer Provides Zero Overhead

Looping Conditional Instruction Execution

Programmable 16-Bit Interval Timer with Prescaler

100-Lead LQFP and 144-Ball Mini-BGA

SYSTEM INTERFACE FEATURES

Flexible I/O Allows 1.8 V, 2.5 V or 3.3 V Operation

All Inputs Tolerate up to 3.6 V Regardless of Mode

16-Bit Internal DMA Port for High-Speed Access to On-

Chip Memory (Mode Selectable)

4M-Byte Memory Interface for Storage of Data Tables

and Program Overlays (Mode Selectable)

8-Bit DMA to Byte Memory for Transparent Program and

Data Memory Transfers (Mode Selectable)

Programmable Memory Strobe and Separate I/O

Memory Space Permits “Glueless” System Design

Programmable Wait State Generation

Two Double-Buffered Serial Ports with Companding

Hardware and Automatic Data Buffering

Automatic Booting of On-Chip Program Memory from

Byte-Wide External Memory, e.g., EPROM, or through

Internal DMA Port

Six External Interrupts

13 Programmable Flag Pins Provide Flexible System

Signaling

UART Emulation through Software SPORT

Reconfiguration

ICE-Port™ Emulator Interface Supports Debugging in

Final Systems

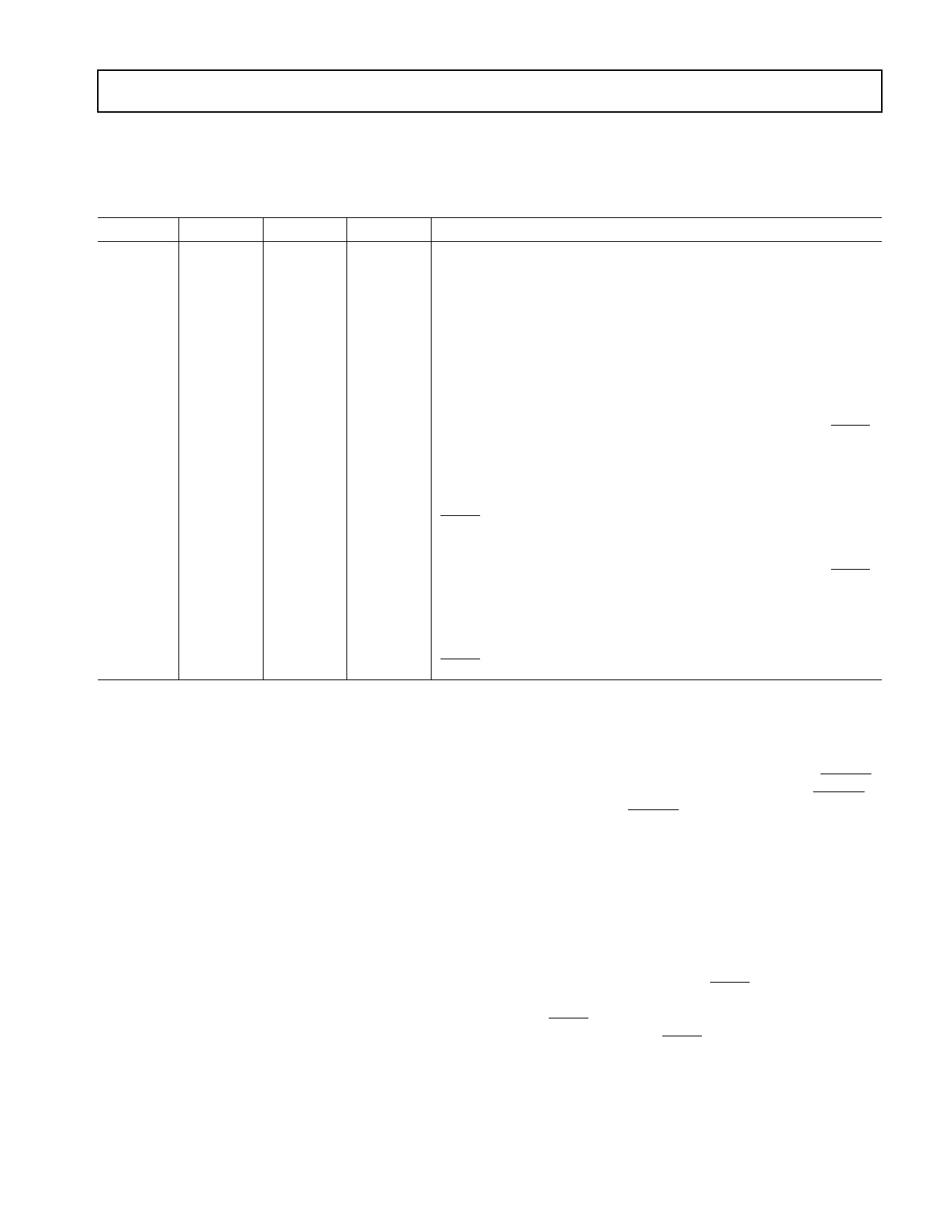

FUNCTIONAL BLOCK DIAGRAM

POWER-DOWN

CONTROL

MEMORY

DATA ADDRESS

GENERATORS

PROGRAM

PROGRAM

MEMORY

UP TO

DATA

MEMORY

UP TO

DAG1 DAG2

Insert chip

blSoEcQkUdENiaCgErRaPmRDOAGhTReAAr4eMM8.EKMM؋EOM2RO4Y-RBAYITDADDRDER5S6ESKSS؋

PROGRAM MEMORY DATA

DATA MEMORY DATA

16-BIT

PROGRAMMABLE

I/O

AND

FLAGS

ARITHMETIC UNITS

ALU

MAC SHIFTER

ADSP-2100 BASE

ARCHITECTURE

SERIAL PORTS

SPORT0 SPORT1

TIMER

FULL MEMORY MODE

EXTERNAL

ADDRESS

BUS

EXTERNAL

DATA

BUS

BYTE DMA

CONTROLLER

OR

EXTERNAL

DATA

BUS

INTERNAL

DMA

PORT

HOST MODE

ICE-Port is a trademark of Analog Devices, Inc.

REV. 0

Information furnished by Analog Devices is believed to be accurate and reli-

able. However, no responsibility is assumed by Analog Devices for its use,

nor for any infringements of patents or other rights of third parties that may

result from its use. No license is granted by implication or otherwise under

any patent or patent rights of Analog Devices.

One Technology Way, P.O.Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel:781/329-4700

http://www.analog.com

Fax:781/326-8703

© Analog Devices, Inc., 2001

1 page

ADSP-218xN Series

Table 2. Common-Mode Pins

Pin Name

# of Pins I/O

Function

RESET

BR

BG

BGH

DMS

PMS

IOMS

BMS

1 I Processor Reset Input

1 I Bus Request Input

1 O Bus Grant Output

1 O Bus Grant Hung Output

1 O Data Memory Select Output

1 O Program Memory Select Output

1 O Memory Select Output

1 O Byte Memory Select Output

CMS

RD

WR

IRQ2

PF7

IRQL1

PF6

IRQL0

PF5

IRQE

PF4

1 O Combined Memory Select Output

1 O Memory Read Enable Output

1 O Memory Write Enable Output

1 I Edge- or Level-Sensitive Interrupt Request1

I/O Programmable I/O pin

1 I Level-Sensitive Interrupt Requests1

I/O Programmable I/O Pin

1 I Level-Sensitive Interrupt Requests1

I/O Programmable I/O Pin

1 I Edge-Sensitive Interrupt Requests1

I/O Programmable I/O Pin

Mode D

PF3

Mode C

PF2

Mode B

PF1

Mode A

PF0

CLKIN

XTAL

CLKOUT

SPORT0

SPORT1

IRQ1–0, FI, FO

PWD

PWDACK

FL0, FL1, FL2

VDDINT

VDDEXT

GND

VDDINT

VDDEXT

1

1

1

1

1

1

1

5

5

1

1

3

2

4

10

4

7

GND

EZ-Port

20

9

I Mode Select Input—Checked Only During RESET

I/O Programmable I/O Pin During Normal Operation

I Mode Select Input—Checked Only During RESET

I/O Programmable I/O Pin During Normal Operation

I Mode Select Input—Checked Only During RESET

I/O Programmable I/O Pin During Normal Operation

I Mode Select Input—Checked Only During RESET

I/O Programmable I/O Pin During Normal Operation

I Clock Input

O Quartz Crystal Output

O Processor Clock Output

I/O Serial Port I/O Pins

I/O Serial Port I/O Pins

Edge- or Level-Sensitive Interrupts, FI, FO2

I Power-Down Control Input

O Power-Down Acknowledge Control Output

O Output Flags

I Internal VDD (1.8 V) Power (LQFP)

I External VDD (1.8 V, 2.5 V, or 3.3 V) Power (LQFP)

I Ground (LQFP)

I Internal VDD (1.8 V) Power (Mini-BGA)

I External VDD (1.8 V, 2.5 V, or 3.3 V) Power (Mini-

BGA)

I Ground (Mini-BGA)

I/O For Emulation Use

1Interrupt/Flag pins retain both functions concurrently. If IMASK is set to enable the corresponding interrupts, the DSP will

vector to the appropriate interrupt vector address when the pin is asserted, either by external devices or set as a programmable

flag.

2SPORT configuration determined by the DSP System Control Register. Software configurable.

REV. 0

–5–

5 Page

ADSP-218xN Series

MODES OF OPERATION

The ADSP-218xN series modes of operation appear in

Table 7.

Table 7. Modes of Operation

Mode D Mode C Mode B Mode A Booting Method

X 0 0 0 BDMA feature is used to load the first 32 program memory words

from the byte memory space. Program execution is held off until all

32 words have been loaded. Chip is configured in Full Memory

Mode.1

X 0 1 0 No automatic boot operations occur. Program execution starts at

external memory location 0. Chip is configured in Full Memory

Mode. BDMA can still be used, but the processor does not automat-

ically use or wait for these operations.

0 1 0 0 BDMA feature is used to load the first 32 program memory words

from the byte memory space. Program execution is held off until all

32 words have been loaded. Chip is configured in Host Mode. IACK

has active pull-down. (Requires additonal hardware.)

0 1 0 1 IDMA feature is used to load any internal memory as desired.

Program execution is held off until the host writes to internal

program memory location 0. Chip is configured in Host Mode.

IACK has active pull-down.1

1 1 0 0 BDMA feature is used to load the first 32 program memory words

from the byte memory space. Program execution is held off until all

32 words have been loaded. Chip is configured in Host Mode; IACK

requires external pull-down. (Requires additonal hardware.)

1 1 0 1 IDMA feature is used to load any internal memory as desired.

Program execution is held off until the host writes to internal

program memory location 0. Chip is configured in Host Mode.

IACK requires external pull-down.1

1Considered as standard operating settings. Using these configurations allows for easier design and better memory management.

Setting Memory Mode

Memory Mode selection for the ADSP-218xN series is

made during chip reset through the use of the Mode C pin.

This pin is multiplexed with the DSP’s PF2 pin, so care must

be taken in how the mode selection is made. The two meth-

ods for selecting the value of Mode C are active and passive.

Passive Configuration

Passive Configuration involves the use of a pull-up or pull-

down resistor connected to the Mode C pin. To minimize

power consumption, or if the PF2 pin is to be used as

an output in the DSP application, a weak pull-up or pull-

down resistance, on the order of 10 k⍀, can be used. This

value should be sufficient to pull the pin to the desired level

and still allow the pin to operate as a programmable flag

output without undue strain on the processor’s output

driver. For minimum power consumption during power-

down, reconfigure PF2 to be an input, as the pull-up or pull-

down resistance will hold the pin in a known state, and will

not switch.

Active Configuration

Active Configuration involves the use of a three-statable

external driver connected to the Mode C pin. A driver’s

output enable should be connected to the DSP’s RESET

signal such that it only drives the PF2 pin when RESET is

active (low). When RESET is deasserted, the driver should

be three-state, thus allowing full use of the PF2 pin as either

an input or output. To minimize power consumption during

power-down, configure the programmable flag as an output

when connected to a three-stated buffer. This ensures that

the pin will be held at a constant level, and will not oscillate

should the three-state driver’s level hover around the logic

switching point.

IDMA ACK Configuration

Mode D = 0 and in host mode: IACK is an active, driven

signal and cannot be “wire ORed.” Mode D = 1 and in host

mode: IACK is an open drain and requires an external

pull-down, but multiple IACK pins can be “wire ORed”

together.

REV. 0

–11–

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ADSP-2188NKST-320.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADSP-2188NKST-320 | DSP Microcomputer | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |