|

|

PDF XRT71D03 Data sheet ( Hoja de datos )

| Número de pieza | XRT71D03 | |

| Descripción | 3 CHANNEL E3/DS3/STS-1 JITTER ATTENUATOR | |

| Fabricantes | Exar | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XRT71D03 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

áç

XRT71D03

SEPTEMBER 2001

3 CHANNEL E3/DS3/STS-1 JITTER ATTENUATOR

REV. 1.2.0

GENERAL DESCRIPTION

The XRT71D03 is a three channel, single chip Jitter

Attenuator, that meets the Jitter transfer characteris-

tics requirements specified in the ETSI TBR-24,

Bellcore GR-499 and GR-253 standards.

In addition, the XRT71D03 also meets the Jitter and

Wander specifications described in the ANSI

T1.105.03b 1997, Bellcore GR-253 and GR-499 stan-

dards.

FEATURES

• Meets the E3/DS3/STS-1 jitter requirements

• No external components required

• Compliant with jitter transfer template outlined in

ITU G.751, G.752, G.755, GR-235-CORE, GR-

499-CORE,1995 standards

• Meets output jitter requirement as specified by

ETSI TBR24

• Meets the Jitter and Wander specifications

described in T1.105.03b,GR-253 and GR-499 stan-

dards.

• Selectable buffer size of 16 and 32 bits

• Jitter attenuator can be disabled

• Available in a 64 pin LQFP package.

• Single 3.3V or 5.0V supply.

• Operates over - 40° C to 85° C temperature range.

APPLICATIONS

• E3/DS3 Access Equipment.

• DSLAMs

FIGURE 1. BLOCK DIAGRAM OF THE XRT71D03

ICT

DJA_n

RClk_n

RClkES

RPOS_n

RNEG_n

FSS

MODE_CTRL

HOST

Reset

Timing Control Block

Phase locked Loop

Write Clock

Read Clock

16/32 Bit FIFO

n = 0, 1, 2

Channel 0

Channel 1

Channel 2

Microprocessor Serial

Interface

XRT71D03

CS SDI SDO SClk

MCLK_n

STS1_n

DS3/E3_n

RRCLK_n

RRPOS_n

RRNEG_n

FL_n

RRCLKES

Exar Corporation 48720 Kato Road, Fremont CA, 94538 • (510) 668-7000 • FAX (510) 668-7017 • www.exar.com

1 page

áç

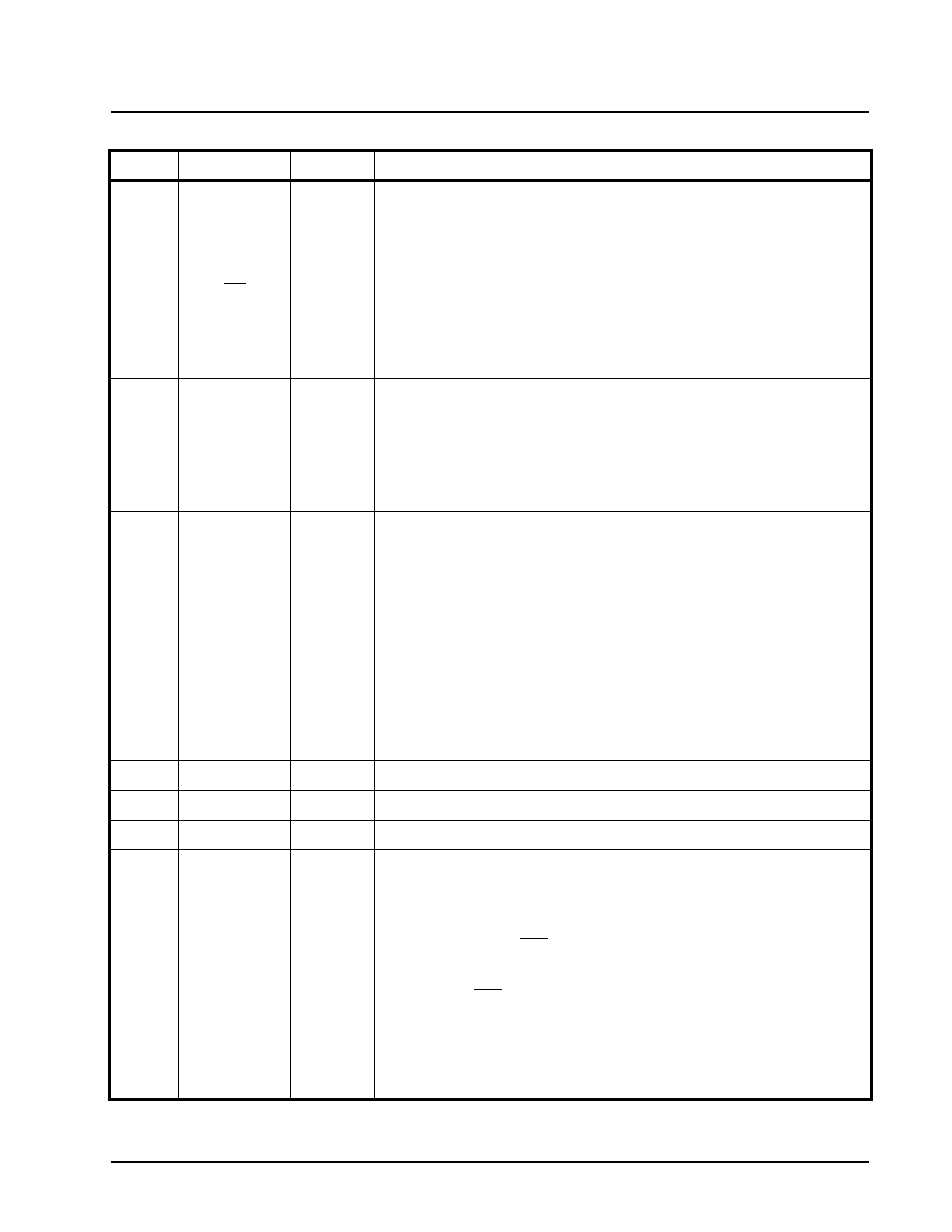

PIN DESCRIPTION

PIN #

11

NAME

MODE_CTRL

12 ICT

13 HOST

14 FLRST

15 GND

16 NC

17 AGND

18 FL_0

19 STS1_0

XRT71D03

3 CHANNEL E3/DS3/STS-1 JITTER ATTENUATOR

REV. 1.2.0

TYPE

I

I

I

I

****

****

O

I

DESCRIPTION

Mode Control:

When “High” in Multimode, all channels are independent. When “Low”, the

Master Channel (channel0) controls DS3/E3_n, STS1_n, RCLKES, FSS and

MCLKn. DJA is NOT affected.

Internal 50 K Ohm pull-up resistor.

In Circuit Testing Input. (Active low):

With this pin tied to ground, all output pins will be in high impedance mode for

in-circuit-testing.

For normal operation this input pin should be tied to VDD.

Internal 50 K Ohm pull-up resistor.

Host/Hardware Mode Select:

An active-high input enables the Host mode. Data is written to the command

registers to configure the XRT71D04.

In the Host mode, the states of discrete input pins are inactive.

An active-low input enables the Hardware Mode.In this mode, the discrete

inputs are active.

Internal 50 K Ohm pull-down resistor.

Fifo Limit Reset

Hardware Mode

Whenever the FIFO is within 2 bits of either underflow or overflow, the FLn) will

be set high.

This pin allows the user to reset the state of FL_n, (FIFO Limit) output pin.

This pin when pulsed “High”, resets the the FL_n output pin, (toggles to GND).

NOTE: The FL_n could be set “High” again if the FIFO is within 2 bits of either

underflow or overflow.

Host Mode

Reading the FL_n bits in the status registers clears the FL_n pin. Master

RESET also clears the FL_n output.

This pin is tied to GND. FLRST has no effect in this mode.

Internal 50 K Ohm pull-down resistor.

Digital Ground

No Connection

Analog Ground

FIFO Limit - channel 0:

This output pin is driven high whenever the internal FIFO comes within two-bits

of being underflow or overflow.

SONET STS1 Mode Select - channel 0:

This pin along with the DS3/E3_0 select pin configures the XRT71D03 either in

E3, DS3 or STS-1 mode.

A table relating to the setting of the pins is given below:

STS-1

DS3/E3

XRT71D03 Operating Mode

0 0 DS3 (44.736 MHz)

0 1 E3 (34.368 MHz)

1 0 STS-1 (51.84 MHz)

1 1 E3 (34.368 MHz)

This input pin is active only in the Hardware Mode

4

5 Page

áç

XRT71D03

3 CHANNEL E3/DS3/STS-1 JITTER ATTENUATOR

REV. 1.2.0

Microprocessor Serial Interface Timing ( see Figure 4 )

Electrical Characteristics (TA = 25°C, VDD = 3.3 V t0 5.0 V± 5 % unless otherwise specified)

SYMBOL

PARAMETER

t21 CS Low to Rising Edge of SClk Setup Time

t22 SClk to CS Hold Time

t23 SDI to Rising Edge of SClk Setup Time

t24 SDI to Rising Edge of SClk Hold Time

t25 SClk “Low” Time

t26 SClk “High” Time

t27 SClk Period

t28 SClk to CSB Hold Time

t29 CS “Inactive” Time

t30 Falling Edge of SClk to SDO Valid Time

t31 Falling Edge of SClk to SDO Invalid Time

t32 Falling Edge of SClk, or rising edge of CS to High Z

MIN

TYP

MAX

UNITS.

50

20

50

50

240

240

500

50

250

200

100

100

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

FIGURE 4. TIMING DIAGRAM FOR THE MICROPROCESSOR SERIAL INTERFACE

CS

SClk

SDI

t21

t22

t23 t24

R/W

t27

t25

t26

A0 A1

t29

t28

CS

SClk

SDO

t30

Hi-Z

SDI

t31

D0

Hi-Z

D1

t33

D2

t32

D7

10

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet XRT71D03.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XRT71D00 | E3/DS3/STS-1 JITTER ATTENUATOR/STS-1 TO DS3 DESYNCHRONIZER | Exar Corporation |

| XRT71D03 | 3 CHANNEL E3/DS3/STS-1 JITTER ATTENUATOR | Exar |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |