|

|

PDF FM24W256 Data sheet ( Hoja de datos )

| Número de pieza | FM24W256 | |

| Descripción | 256-Kbit (32 K x 8) Serial (I2C) F-RAM | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de FM24W256 (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

FM24W256

256-Kbit (32 K × 8) Serial (I2C) F-RAM

256-Kbit (32 K × 8) Serial (I2C) F-RAM

Features

■ 256-Kbit ferroelectric random access memory (F-RAM)

logically organized as 32 K × 8

❐ High-endurance 100 trillion (1014) read/writes

❐ 151-year data retention (See the Data Retention and

Endurance table)

❐ NoDelay™ writes

❐ Advanced high-reliability ferroelectric process

■ Fast 2-wire Serial interface (I2C)

❐ Up to 1-MHz frequency

❐ Direct hardware replacement for serial (I2C) EEPROM

❐ Supports legacy timings for 100 kHz and 400 kHz

■ Low power consumption

❐ 100 A active current at 100 kHz

❐ 15 A (typ) standby current

■ Wide voltage operation: VDD = 2.7 V to 5.5 V

■ Industrial temperature: –40 C to +85 C

■ 8-pin small outline integrated circuit (SOIC) package

■ Restriction of hazardous substances (RoHS) compliant

Functional Description

The FM24W256 is a 256-Kbit nonvolatile memory employing an

advanced ferroelectric process. A ferroelectric random access

memory or F-RAM is nonvolatile and performs reads and writes

similar to a RAM. It provides reliable data retention for 151 years

while eliminating the complexities, overhead, and system-level

reliability problems caused by EEPROM and other nonvolatile

memories.

Unlike EEPROM, the FM24W256 performs write operations at

bus speed. No write delays are incurred. Data is written to the

memory array immediately after each byte is successfully

transferred to the device. The next bus cycle can commence

without the need for data polling. In addition, the product offers

substantial write endurance compared with other nonvolatile

memories. Also, F-RAM exhibits much lower power during writes

than EEPROM since write operations do not require an internally

elevated power supply voltage for write circuits. The FM24W256

is capable of supporting 1014 read/write cycles, or 100 million

times more write cycles than EEPROM.

These capabilities make the FM24W256 ideal for nonvolatile

memory applications, requiring frequent or rapid writes.

Examples range from data logging, where the number of write

cycles may be critical, to demanding industrial controls where the

long write time of EEPROM can cause data loss. The

combination of features allows more frequent data writing with

less overhead for the system.

The FM24W256 provides substantial benefits to users of serial

(I2C) EEPROM as a hardware drop-in replacement. The device

specifications are guaranteed over an industrial temperature

range of –40 C to +85 C.

For a complete list of related documentation, click here.

Logic Block Diagram

Counter

Address

Latch

15

SDA

SCL

WP

A2-A0

Serial to Parallel

Converter

Control Logic

8

32 K x 8

F-RAM Array

8

Data Latch

Cypress Semiconductor Corporation • 198 Champion Court

Document Number: 001-84464 Rev. *J

• San Jose, CA 95134-1709 • 408-943-2600

Revised October 7, 2015

1 page

FM24W256

full pagewidth

SDA

Figure 3. START and STOP Conditions

SDA

SCL

S

START Condition

P

STOP Condition

SCL

handbook, full pagewidth

SDA

MSB

Figure 4. Data Transfer on the I2C Bus

Acknowledgement

signal from slave

P

Acknowledgement S

signal from receiver

SCL

S

1

START

condition

2

789

ACK

Byte complete

1

2 3 4-8

9

ACK

S

or

P

STOP or

START

condition

Data/Address Transfer

All data transfers (including addresses) take place while the SCL

signal is HIGH. Except under the three conditions described

above, the SDA signal should not change while SCL is HIGH.

Acknowledge / No-acknowledge

The acknowledge takes place after the 8th data bit has been

transferred in any transaction. During this state the transmitter

should release the SDA bus to allow the receiver to drive it. The

receiver drives the SDA signal LOW to acknowledge receipt of

the byte. If the receiver does not drive SDA LOW, the condition

is a no-acknowledge and the operation is aborted.

The receiver would fail to acknowledge for two distinct reasons.

First is that a byte transfer fails. In this case, the no-acknowledge

ceases the current operation so that the device can be

addressed again. This allows the last byte to be recovered in the

event of a communication error.

Second and most common, the receiver does not acknowledge

to deliberately end an operation. For example, during a read

operation, the FM24W256 will continue to place data onto the

bus as long as the receiver sends acknowledges (and clocks).

When a read operation is complete and no more data is needed,

the receiver must not acknowledge the last byte. If the receiver

acknowledges the last byte, this will cause the FM24W256 to

attempt to drive the bus on the next clock while the master is

sending a new command such as STOP.

Figure 5. Acknowledge on the I2C Bus

handbook, full pagewidth

DATA OUTPUT

BY MASTER

DATA OUTPUT

BY SLAVE

No Acknowledge

Acknowledge

SCL FROM

MASTER

S

START

Condition

1

2

89

Clock pulse for

acknowledgement

Document Number: 001-84464 Rev. *J

Page 5 of 18

5 Page

FM24W256

AC Switching Characteristics

Over the Operating Range

Parameter[4]

Alt.

Parameter

Description

fSCL[5]

SCL clock frequency

tSU; STA

Start condition setup for repeated Start

tHD;STA

Start condition hold time

tLOW

Clock LOW period

tHIGH

Clock HIGH period

tSU;DAT

tSU;DATA Data in setup

tHD;DAT

tHD;DATA Data in hold

tDH Data output hold (from SCL @ VIL)

tR[6] tr Input rise time

tF[6] tf Input fall time

tSU;STO

STOP condition setup

tAA tVD;DATA SCL LOW to SDA Data Out Valid

tBUF Bus free before new transmission

tSP Noise suppression time constant on SCL, SDA

Min Max Min

– 0.1 –

4.7 – 0.6

4.0 – 0.6

4.7 – 1.3

4.0 – 0.6

250 – 100

0–0

0–0

– 1000 –

– 300 –

4.0 – 0.6

–3–

4.7 – 1.3

– 50 –

Max

0.4

–

–

–

–

–

–

–

300

300

–

0.9

–

50

Min

–

0.25

0.25

0.6

0.4

100

0

0

–

–

0.25

–

0.5

–

Max Unit

1.0 MHz

– s

– s

– s

– s

– ns

– ns

– ns

300 ns

100 ns

– s

0.55 s

– s

50 ns

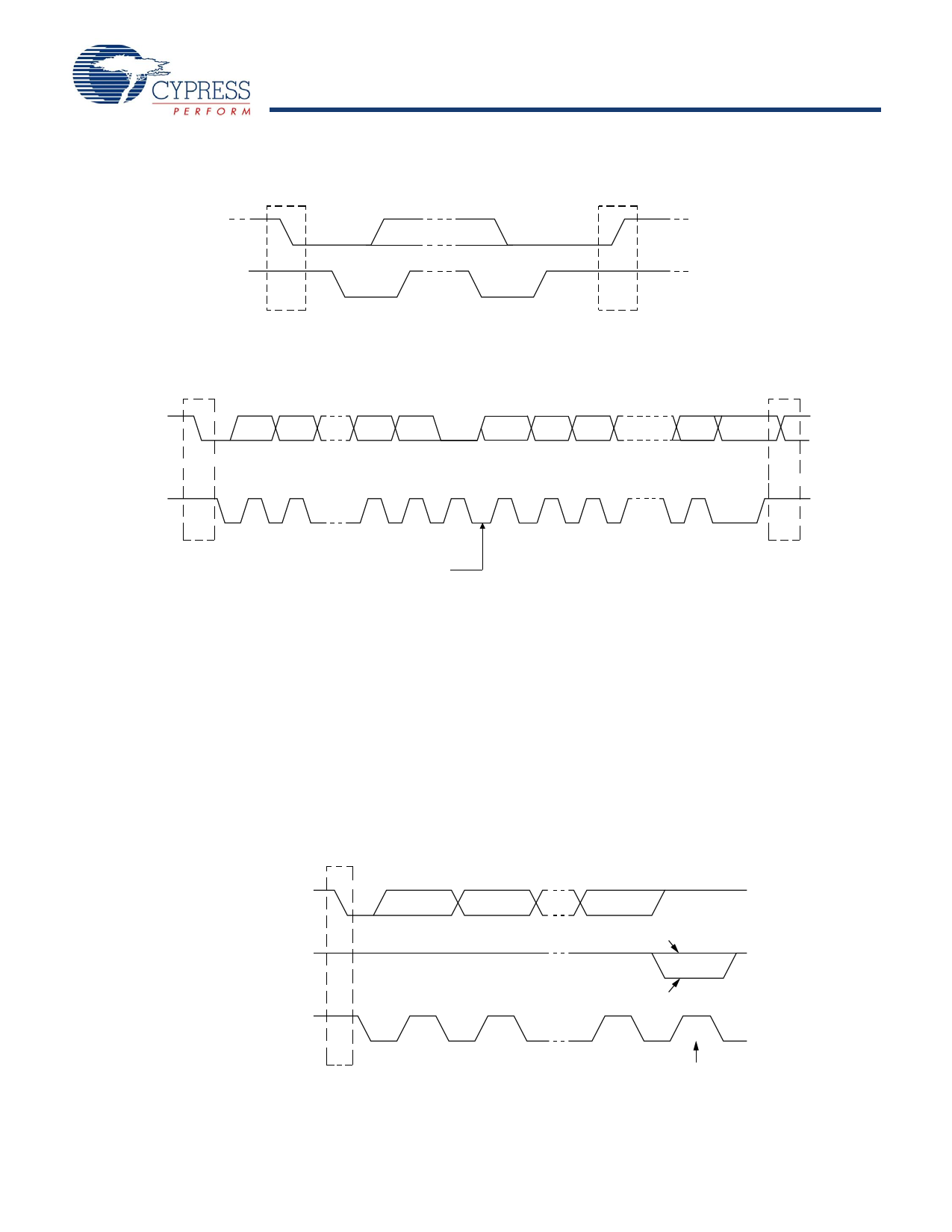

SCL

SDA

tSU:SDA

Start

SCL

SDA

Figure 13. Read Bus Timing Diagram

`tR

tHIGH

tF

tLOW

tBUF 1/fSCL

Stop Start

tAA tDH

Figure 14. Write Bus Timing Diagram

tHD:DAT

tSP

tHD:DAT

tSU:DAT

Acknowledge

tSU:STO

tHD:STA

tSU:DAT

tAA

tSP

Start

Stop Start

Acknowledge

Notes

4. Test conditions assume signal transition time of 10 ns or less, timing reference levels of VDD/2, input pulse levels of 0 to VDD(typ), and output loading of the specified

IOL and load capacitance shown in Figure 12.

5. The speed-related specifications are guaranteed characteristic points along a continuous curve of operation from DC to fSCL (max).

6. These parameters are guaranteed by design and are not tested.

Document Number: 001-84464 Rev. *J

Page 11 of 18

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet FM24W256.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| FM24W256 | 256-Kbit (32 K x 8) Serial (I2C) F-RAM | Cypress Semiconductor |

| FM24W256 | 256Kb Wide Voltage Serial F-RAM | Ramtron |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |