|

|

PDF UPD411A-2 Data sheet ( Hoja de datos )

| Número de pieza | UPD411A-2 | |

| Descripción | 4096-BIT DYNAMIC RAMS | |

| Fabricantes | NEC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UPD411A-2 (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

NEe Microcomputers, Inc.

NEe

Jl.PD411A

Jl.PD411A-1

Jl.PD411A-2

DESCR IPTION

4096 BIT DYNAMIC RAMS

The ,uPD411A Famify consists of four 4096 words by 1 bit dynamic N-channel MOS

RAMs. They are designed for memory applications where very low cost and large bit

storage are important design objectives. The ,uPD411 A Family is designed using

dynamic circuitry which reduces the standby power dissipation.

Reading information from the memory is non·destructive. Refreshing is easily

II

accomplished by performing one read cycle on each of the 64 row addresses. Each

row address must be refreshed every two milliseconds. The memory is refreshed whether

Chip Select is a logic high or a logic low.

FEATURES

• Low Standby Power

• 4096 words x 1 bit Organization

• A single low·capacitance high level clock input with solid ±1 volt margins.

• Inactive Power 0.7 mW (Typ.)

• Power Supply +12, +5, -5V

• Easy System Interface

• TTL Compatible (Except CE)

• Address Registers on the Chip

• Simple Memory Expansion by Chip Select

• Three State Output and TTL Compatible

• 22 pin Plastic Dual·in-Line Package

• Replacement for INTEL's 21078, TI's 4060 and Equivalent Devices.

• 3 Performance Ranges:

~PD411A

~PD411A·l

~PD411A·2

ACCESS TIME

300 ns

250 ns

200 ns

RfW CYCLE

470 ns

430 ns

400 ns

RMWCYCLE REFRESH TIME

65Uns

600ns

520 ns

2m.

2m.

2m,

PIN CONFIGURATION

VBB

Ag

A10

A11

Cs

DIN

DOUT

AO

"1

A2

VCC

Vss

AS

A7

AS

VOD

CE

NC

A5

A4

.4.3

WE

Rev/1

PIN NAMES

AO' All

AO-AS

CE

Address Inputs

Refresh Addresses

ChiD Enable

CS Chip Select

DIN Data Inpl..It

DOUT

WE

Data O"tput

Write Enable

VOD

Vce

VSS

Vas

INC

Power (+12V)

Powe, (+5V)

Ground

(Pow... -5V)

No Connection

19

1 page

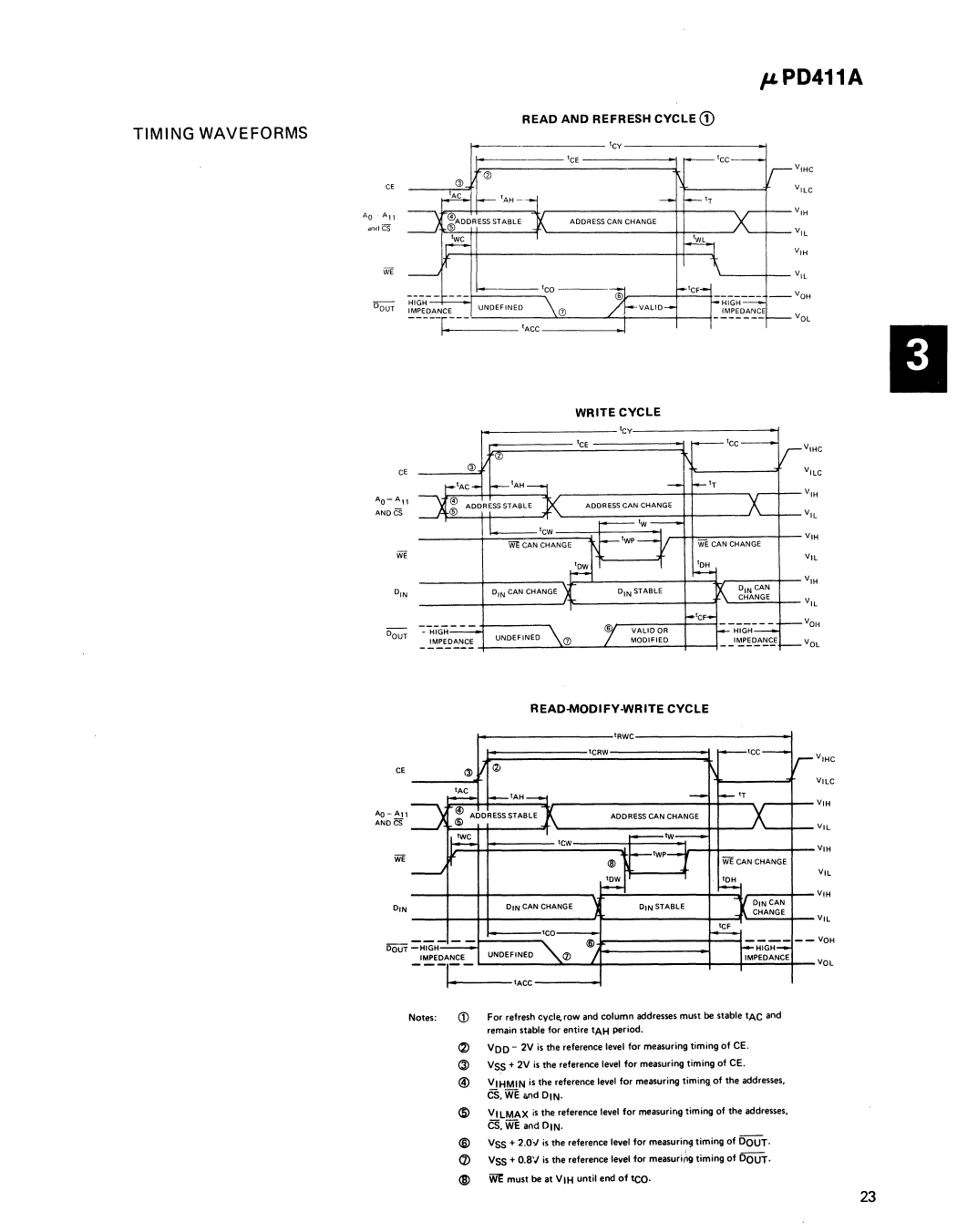

TIMING WAVEFORMS

Cf

CDREAD AND REFRESH CYCLE

fLPD411A

WRITE CYCLE

Cf

-----l-~~=~':::=::::jct=;;;;;_=:J r-++~----,-::-+_- V,H

_ _ _ _~-----,~~L------+_-~r_-~_+---V,H

VIL-----l-------',"jc--------+--.f '-....:::.=~+--

CE

AO- All

AND CS

R EAD-MOD I FY-WR ITE CYC LE

-----t---++--------------,.k-~-----~~~.r_--+_-VIH

DIN ---r--++--------r~---------~~~~~~+_-VIL

L-_ _ _ _ _ _~~__'~---------~--~~~~--VOL

~----- tACC - - - - - _

Notes:

CD For refresh cycle. row and column addresses must be stable tAC and

remain stable for entire tAH period.

(2) VOO - 2V is the reference level for measuring timing of CEo

(l) VSS + 2V is the reference level for measuring timing of CEo

® VIHMIN is the reference level for measuring timing of the addresses,

CS. WE and DIN.

@ VILMAX is the reference level for measuring timing of the addresses,

CS. WE and DIN.

@ VSS + 2.0'", is the reference level for measuring timing of DOUT·

(j) VSS + O.8'J is the reference level for measuring timing of DOUT·

<B> ~ must be at VIH until end of teO·

23

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet UPD411A-2.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UPD411A-1 | 4096-BIT DYNAMIC RAMS | NEC |

| UPD411A-2 | 4096-BIT DYNAMIC RAMS | NEC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |