|

|

PDF MAX11167 Data sheet ( Hoja de datos )

| Número de pieza | MAX11167 | |

| Descripción | SAR ADC | |

| Fabricantes | Maxim Integrated | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MAX11167 (archivo pdf) en la parte inferior de esta página. Total 28 Páginas | ||

|

No Preview Available !

EVALUATION KIT AVAILABLE

MAX11167

16-Bit, 250ksps, ±5V SAR ADC with Internal

Reference in TDFN

General Description

The MAX11167 16-bit, 250ksps, SAR ADC offers excel-

lent AC and DC performance with true bipolar input range,

small size, and internal reference. The MAX11167 mea-

sures a Q5V (10VP-P) input range while operating from

a single 5V supply. A patented charge-pump architecture

allows direct sampling of high-impedance sources. The

MAX11167 integrates an optional 6.7ppm/NC reference

with internal buffer, saving the cost and space of an exter-

nal reference.

This ADC achieves 93.2dB SNR and -102.5dB THD. The

MAX11167 guarantees 16-bit no-missing codes and Q0.5

LSB INL (typ).

The MAX11167 communicates using an SPI-compatible

serial interface at 2.5V, 3V, 3.3V, or 5V logic. The serial

interface can be used to daisy-chain multiple ADCs in

parallel for multichannel applications and provides a busy

indicator option for simplified system synchronization and

timing.

The MAX11167 is offered in a 12-pin, 3mm x 3mm, TDFN

package and is specified over the -40NC to +85NC tem-

perature range.

Applications

● Data Acquisition Systems

● Industrial Control Systems/Process Control

● Medical Instrumentation

● Automatic Test Equipment

Typical Operating Circuit

VDD

(5V)

1µF

VOVDD

(2.3V TO 5V)

1µF

MAX9632

±5V

10Ω AIN+

AIN-

4.7nF

REF

10µF

16-BIT ADC

INTERFACE

AND

CONTROL

MAX11167

SCLK

DIN

DOUT

CNVST

HOST

µC

REF

BUF

AGNDS

INTERNAL

REFERENCE

GND

REFIO

0.1µF

Benefits and Features

● High DC/AC Accuracy Improves Measurement

Quality

• 16-Bit Resolution with No Missing Codes

• 250ksps Throughput Rate Without Pipeline Delay/

Latency

• 93.2dB SNR and -102.5dB THD at 10kHz

• 0.5 LSBRMS Transition Noise

• ±0.2 LSB DNL (typ) and ±0.4 LSB INL (typ)

● Highly Integrated ADC Saves Cost and Space

• ±6.7ppm/°C Internal Reference

• Internal Reference Buffer

● Wide Supply Range and Low Power Simplify Power-

Supply Design

• 5V Analog Supply

• 2.3V to 5V Digital Supply

• 21.2mW Power Consumption at 250ksps

• 10μA in Shutdown Mode

● Multi-Industry Standard Serial Interface and Small

Package Reduce Size

• SPI/QSPI™/MICROWIRE®/DSP-Compatible

Serial Interface

• 3mm x 3mm Tiny 12-Pin TDFN Package

QSPI is a trademark of Motorola, Inc.

MICROWIRE is a registered trademark of National

Semiconductor Corporation.

14-Bit to 18-Bit SAR ADC Family

±5V Input

Internal

Reference

0 to 5V Input

Internal

Reference

0 to 5V Input

External

Reference

14-BIT

500ksps

16-BIT

250ksps

16-BIT

18-BIT

500ksps 500ksps

—

MAX11167 MAX11166 MAX11156

MAX11169 MAX11168 MAX11158

—

MAX11161 MAX11160 MAX11150

MAX11165 MAX11164 MAX11154

MAX11262 MAX11163 MAX11162 MAX11152

Selector Guide and Ordering Information appear at end of

data sheet.

19-6445; Rev 4; 5/15

1 page

MAX11167

16-Bit, 250ksps, ±5V SAR ADC

with Internal Reference in TDFN

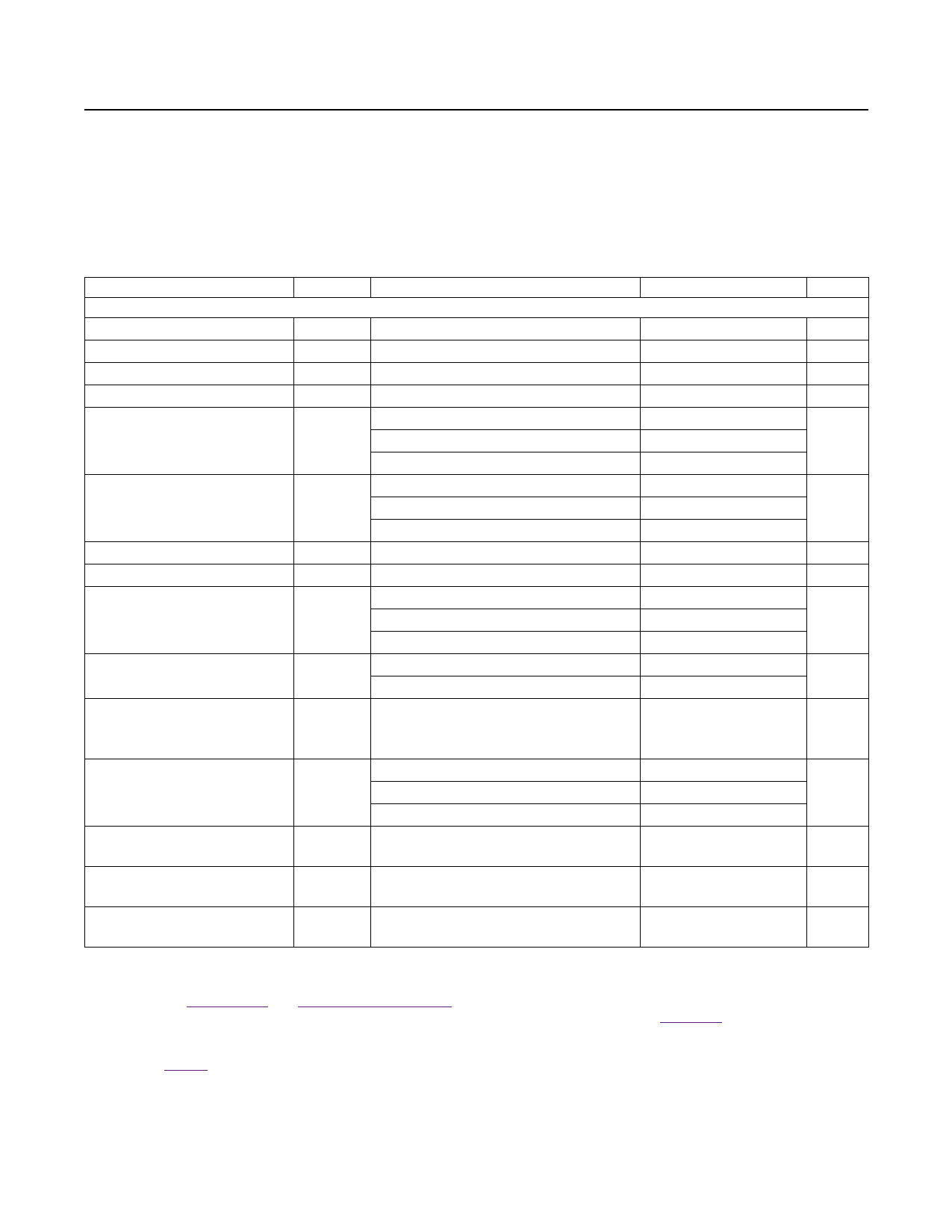

Electrical Characteristics (continued)

(VDD = 4.75V to 5.25V, VOVDD = 2.3V to 5.25V, fSAMPLE = 250ksps, VREF = 4.096V; TA = TMIN to TMAX, unless otherwise noted.

Typical values are at TA = +25NC.) (Note 2)

PARAMETER

TIMING (Note 9)

Time Between Conversions

Conversion Time

Acquisition Time

CNVST Pulse Width

SCLK Period (CS Mode)

SCLK Period (Daisy-Chain Mode)

SCLK Low Time

SCLK High Time

SCLK Falling Edge to Data Valid

Delay

CNVST Low to DOUT D15 MSB

Valid (CS Mode)

SYMBOL

tCYC

tCONV

tACQ

tCNVPW

tSCLK

tSCLK

tSCLKL

tSCLKH

tDDO

tEN

CONDITIONS

CNVST rising to data available

tACQ = tCYC - tCONV

CS mode

VOVDD > 4.5V

VOVDD > 2.7V

VOVDD > 2.3V

VOVDD > 4.5V

VOVDD > 2.7V

VOVDD > 2.3V

VOVDD > 4.5V

VOVDD > 2.7V

VOVDD > 2.3V

VOVDD > 2.7V

VOVDD < 2.7V

MIN TYP MAX UNITS

4 100000 µs

2.7 3.0 µs

1 µs

5 ns

14

20 ns

26

16

24 ns

30

5 ns

5 ns

12

18 ns

23

14

ns

17

CNVST High or Last SCLK

Falling Edge to DOUT High

Impedance

tDIS CS Mode

20 ns

DIN Valid Setup Time from SCLK

Falling Edge

DIN Valid Hold Time from SCLK

Falling Edge

tSDINSCK

VOVDD > 4.5V

VOVDD > 2.7V

VOVDD > 2.3V

tHDINSCK

3

5 ns

6

0 ns

SCLK Valid Setup Time to

CNVST Falling Edge

tSSCKCNF

3 ns

SCLK Valid Hold Time to CNVST

Falling Edge

tHSCKCNF

6 ns

Note 2: Maximum and minimum limits are fully production tested over specified supply voltage range and at a temperature of

+25°C. Limits over the operating temperature range are guaranteed by design and device characterization.

Note 3: See the Analog Inputs and Overvoltage Input Clamps sections.

Note 4: Static Performance limits are guaranteed by design and device characterization, see the Definitions section.

Note 5: Defined as the change in positive full-scale code transition caused by a Q5% variation in the VDD supply voltage.

Note 6: 10kHz sine wave input, -0.1dB below full scale.

Note 7: See Table 4 for definition of the reference modes.

Note 8: fIN1 ~ 9.4kHz, fIN2 ~ 10.7kHz, Each tone at -6.1dB below full scale.

Note 9: CLOAD = 65pF on DOUT.

www.maximintegrated.com

Maxim Integrated │ 5

5 Page

MAX11167

Pin Configuration

16-Bit, 250ksps, ±5V SAR ADC

with Internal Reference in TDFN

TOP VIEW

REFIO 1

REF 2

VDD 3

AIN+ 4

AIN- 5

GND 6

MAX11167

EP

TDFN

12 AGNDS

11 OVDD

10 DIN

9 SCLK

8 DOUT

7 CNVST

Pin Description

PIN NAME

I/O

1

REFIO

I/O

2

REF

I/O

3 VDD I

4 AIN+

5 AIN-

6 GND

I

I

I

7 CNVST I

8 DOUT O

9 SCLK I

10 DIN

I

11 OVDD

I

12 AGNDS

I

— EP —

FUNCTION

External Reference Input/Internal Reference Output. Place a 0.1µF capacitor from REFIO to

AGNDS.

External Reference Input/Reference Buffer Decoupling. Bypass to AGNDS in close proximity with a

X5R or X7R 10µF 16V capacitor. See the Layout, Grounding, and Bypassing section.

Analog Power Supply. Bypass to GND with a 0.1µF capacitor for each device and one 10µF

per PCB.

Positive Analog Input

Negative Analog Input. Connect AIN- to the analog ground plane or to a remote-sense ground.

Power-Supply Ground

Convert Start Input. The rising edge of CNVST initiates conversions. The falling edge of CNVST

with SCLK high enables the serial interface.

Serial Data Output. DOUT will change stated on the falling edge of SCLK.

Serial Clock Input. Clocks data out of the serial interface when the device is selected.

Serial Data Input. DIN data is latched into the serial interface on the rising edge of SCLK.

Digital Power Supply. Bypass to GND with a 0.1µF capacitor for each device and one 10µF

per PCB.

Analog Ground Sense. Zero current reference for the on-board DAC and reference source.

Reference for REFIO and REF.

Exposed Pad. Connect to PCB GND.

www.maximintegrated.com

Maxim Integrated │ 11

11 Page | ||

| Páginas | Total 28 Páginas | |

| PDF Descargar | [ Datasheet MAX11167.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MAX1116 | (MAX1115 / MAX1116) Single-Supply / Low-Power / Serial 8-Bit ADCs | Maxim Integrated |

| MAX11160 | SAR ADC | Maxim Integrated |

| MAX11161 | SAR ADC | Maxim Integrated |

| MAX11162 | SAR ADC | Maxim Integrated |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |