|

|

PDF KSZ8895MLUB Data sheet ( Hoja de datos )

| Número de pieza | KSZ8895MLUB | |

| Descripción | Integrated 5-Port 10/100 Managed Switch | |

| Fabricantes | Micrel Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de KSZ8895MLUB (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

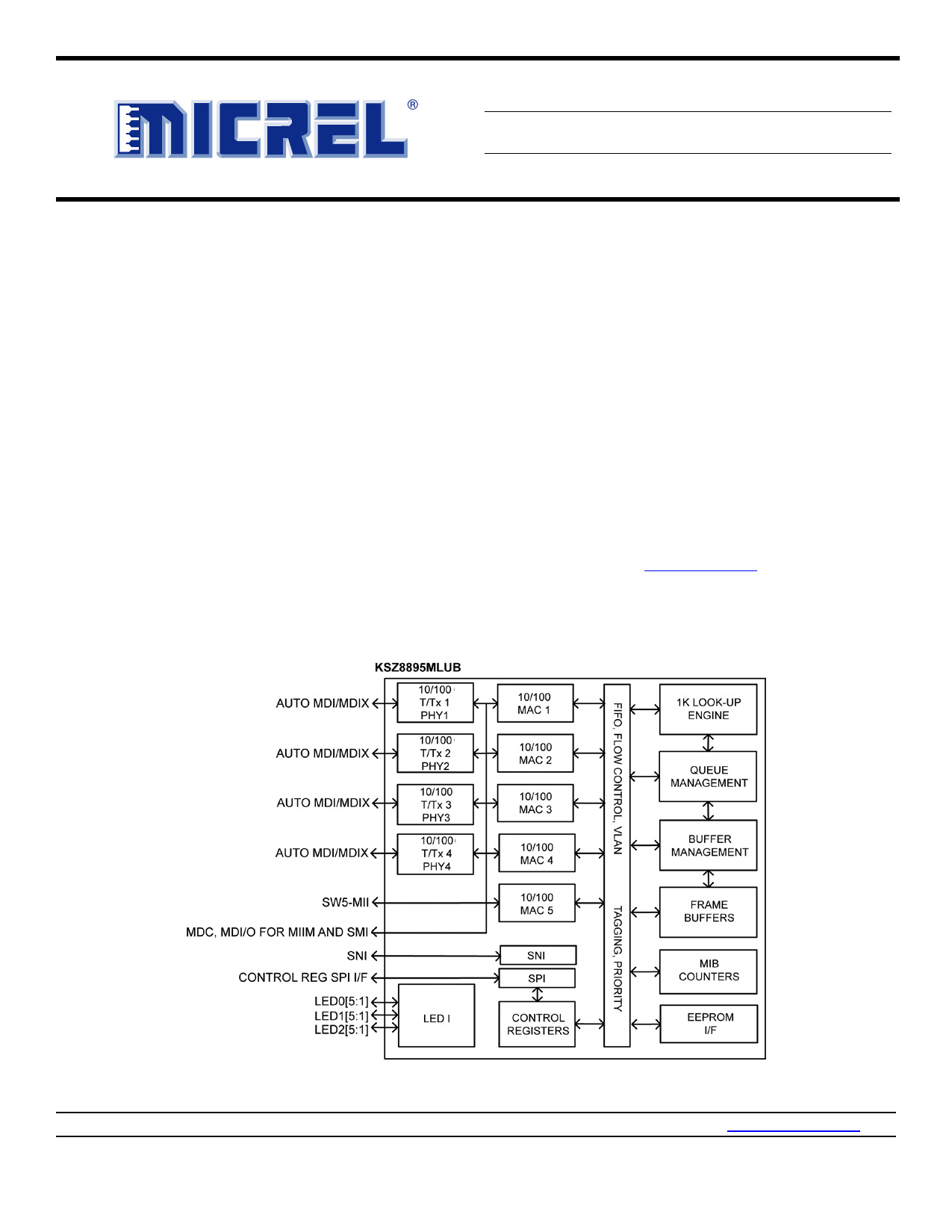

General Description

The KSZ8895MLUB is a highly-integrated Layer 2-

managed 5-port switch with an optimized design and

plentiful features, qualified to meet AEC-Q100 standard

for automotive applications. It is designed for cost-

sensitive 10/100Mbps 5-port switch systems with on-chip

termination, lowest power consumption and internal core

power controller. These features will save more system

cost. It has 1.4Gbps high-performance memory

bandwidth, shared memory based switch fabric with full

non-blocking configuration. It also provides an extensive

feature set such as power management, programmable

rate limit and priority ratio, tag/port-based VLAN, packets

filtering, quality-of-service (QoS) four-queue

prioritization, management interface, and MIB counters.

Port 5 is a MAC 5 MII interface with PHY mode as

default at switch side. The SW5-MII interface can be

connected to a processor with a MAC MII interface.

Functional Diagram

KSZ8895MLUB

Integrated 5-Port 10/100 Managed Switch

Revision 2.1

The KSZ8895MLUB consists of 10/100 PHYs with

patented and enhanced mixed-signal technology, media

access control (MAC) units, a high-speed non-blocking

switch fabric, a dedicated address lookup engine, and an

on-chip frame buffer memory. The KSZ8895MLUB

contains five MACs and four integrated PHYs. All PHYs

support 10/100Base-T/TX.

All registers of MACs and PHYs units can be managed

by the SPI interface or the SMI interface. MIIM registers

of the PHYs can be accessed through the MDC/MDIO

interface. EEPROM can set all control registers for the

unmanaged mode.

The KSZ8895MLUB provides multiple CPU control/data

interfaces to effectively address both current and

emerging fast Ethernet applications.

Datasheets and support documentation are available on

Micrel’s web site at: www.micrel.com.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

April 1, 2014

Revision 2.1

1 page

Micrel, Inc.

KSZ8895MLUB

Advanced Functionality...................................................................................................................................................... 39

QoS Priority Support ......................................................................................................................................................... 39

Port-Based Priority............................................................................................................................................................ 39

802.1p-Based Priority ....................................................................................................................................................... 39

Spanning Tree Support..................................................................................................................................................... 40

Rapid Spanning Tree Support .......................................................................................................................................... 41

Tail Tagging Mode ............................................................................................................................................................ 41

IGMP Support ................................................................................................................................................................... 42

Port Mirroring Support ...................................................................................................................................................... 43

VLAN Support ................................................................................................................................................................... 43

Rate Limiting Support ....................................................................................................................................................... 44

Ingress Rate Limit ............................................................................................................................................................. 44

Egress Rate Limit.............................................................................................................................................................. 44

Transmit Queue Ratio Programming ................................................................................................................................ 45

Filtering for Self-Address, Unknown Unicast/Multicast Address and Unknown VID Packet/IP Multicast ........................ 45

Configuration Interfaces..................................................................................................................................................... 46

I2C Master Serial Bus Configuration ................................................................................................................................. 46

SPI Slave Serial Bus Configuration .................................................................................................................................. 46

MII Management Interface (MIIM) .................................................................................................................................... 49

Serial Management Interface (SMI).................................................................................................................................. 49

Register Description ........................................................................................................................................................... 51

Global Registers.................................................................................................................................................................. 53

Register 0 (0×00): Chip ID0 .............................................................................................................................................. 53

Register 1 (0×01): Chip ID1 / Start Switch........................................................................................................................ 53

Register 2 (0×02): Global Control 0 .................................................................................................................................. 53

Register 2 (0×02): Global Control 0 .................................................................................................................................. 54

Register 3 (0×03): Global Control 1 .................................................................................................................................. 54

Register 3 (0×03): Global Control 1 .................................................................................................................................. 55

Register 4 (0×04): Global Control 2 .................................................................................................................................. 56

Register 4 (0×04): Global Control 2 .................................................................................................................................. 57

Register 5 (0×05): Global Control 3 .................................................................................................................................. 57

Register 6 (0×06): Global Control 4 .................................................................................................................................. 58

Register 7 (0×07): Global Control 5 .................................................................................................................................. 59

Register 8 (0×08): Global Control 6 .................................................................................................................................. 59

Register 9 (0×09): Global Control 7 .................................................................................................................................. 59

Register 10 (0×0A): Global Control 8................................................................................................................................ 59

April 1, 2014

5 Revision 2.1

5 Page

Micrel, Inc.

KSZ8895MLUB

Register 248 (0xF8): Port 5 Priority 1 Ingress Limit Control 2 .......................................................................................... 87

Register 185 (0xB9): Port 1 Priority 2 Ingress Limit Control 3.......................................................................................... 87

Register 201 (0xC9): Port 2 Priority 2 Ingress Limit Control 3.......................................................................................... 87

Register 217 (0xD9): Port 3 Priority 2 Ingress Limit Control 3.......................................................................................... 87

Register 233 (0xE9): Port 4 Priority 2 Ingress Limit Control 3.......................................................................................... 87

Register 249 (0xF9): Port 5 Priority 2 Ingress Limit Control 3 .......................................................................................... 87

Register 186 (0xBA): Port 1 Priority 3 Ingress Limit Control 4 ......................................................................................... 88

Register 202 (0xCA): Port 2 Priority 3 Ingress Limit Control 4 ......................................................................................... 88

Register 218 (0xDA): Port 3 Priority 3 Ingress Limit Control 4 ......................................................................................... 88

Register 234 (0xEA): Port 4 Priority 3 Ingress Limit Control 4 ......................................................................................... 88

Register 250 (0xFA): Port 5 Priority 3 Ingress Limit Control 4.......................................................................................... 88

Register 187 (0xBB): Port 1 Queue 0 Egress Limit Control 1 .......................................................................................... 88

Register 203 (0xCB): Port 2 Queue 0 Egress Limit Control 1 .......................................................................................... 88

Register 219 (0xDB): Port 3 Queue 0 Egress Limit Control 1 .......................................................................................... 88

Register 235 (0xEB): Port 4 Queue 0 Egress Limit Control 1 .......................................................................................... 88

Register 251 (0xFB): Port 5 Queue 0 Egress Limit Control 1........................................................................................... 88

Register 188 (0xBC): Port 1 Queue 1 Egress Limit Control 2 .......................................................................................... 88

Register 204 (0xCC): Port 2 Queue 1 Egress Limit Control 2 .......................................................................................... 88

Register 220 (0xDC): Port 3 Queue 1 Egress Limit Control 2 .......................................................................................... 88

Register 236 (0xEC): Port 4 Queue 1 Egress Limit Control 2 .......................................................................................... 88

Register 252 (0xFC): Port 5 Queue 1 Egress Limit Control 2 .......................................................................................... 88

Register 189 (0xBD): Port 1 Queue 2 Egress Limit Control 3 .......................................................................................... 89

Register 205 (0xCD): Port 2 Queue 2 Egress Limit Control 3 .......................................................................................... 89

Register 221 (0xDD): Port 3 Queue 2 Egress Limit Control 3 .......................................................................................... 89

Register 237 (0xED): Port 4 Queue 2 Egress Limit Control 3 .......................................................................................... 89

Register 253 (0xFD): Port 5 Queue 2 Egress Limit Control 3 .......................................................................................... 89

Register 190 (0xBE): Port 1 Queue 3 Egress Limit Control 4 .......................................................................................... 89

Register 206 (0xCE): Port 2 Queue 3 Egress Limit Control 4 .......................................................................................... 89

Register 222 (0xDE): Port 3 Queue 3 Egress Limit Control 4 .......................................................................................... 89

Register 238 (0xEE): Port 4 Queue 3 Egress Limit Control 4 .......................................................................................... 89

Register 254 (0xFE): Port 5 Queue 3 Egress Limit Control 4........................................................................................... 89

Register 191(0xBF): Testing Register .............................................................................................................................. 91

Register 207(0xCF): Reserved Control Register............................................................................................................. 91

Register 223(0xDF): Test Register 2 ................................................................................................................................ 91

Register 239(0xEF): Test Register 3 ................................................................................................................................ 91

Register 255(0xFF): Testing Register4............................................................................................................................. 91

April 1, 2014

11 Revision 2.1

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet KSZ8895MLUB.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| KSZ8895MLU | Integrated 5-Port 10/100 Managed Switch | Micrel Semiconductor |

| KSZ8895MLUB | Integrated 5-Port 10/100 Managed Switch | Micrel Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |