|

|

PDF CD40105BMS Data sheet ( Hoja de datos )

| Número de pieza | CD40105BMS | |

| Descripción | CMOS FIFO Register | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CD40105BMS (archivo pdf) en la parte inferior de esta página. Total 10 Páginas | ||

|

No Preview Available !

CD40105BMS

December 1992

CMOS FIFO Register

Features

Description

• 4 Bits x 16 Words

• High Voltage Type (20V Rating)

• Independent Asynchronous Inputs and Outputs

• 3-State Outputs

• Expandable in Either Direction

• Status Indicators on Input and Output

• Reset Capability

• Standardized Symmetrical Output Characteristics

• 100% Tested for Quiescent Current at 20V

• 5V, 10V and 15V Parametric Ratings

• Maximum Input Current of 1µA at 18V Over Full Pack-

age Temperature Range; 100nA at 18V and +25oC

• Noise Margin (Over Full Package/Temperature Range)

- 1V at VDD = 5V

- 2V at VDD = 10V

- 2.5V at VDD = 15V

• Meets All Requirements of JEDEC Tentative Standard

No. 13B, “Standard Specifications for Description of

‘B’ Series CMOS Devices”

Applications

• Bit Rate Smoothing

• CPU/Terminal Buffering

• Data Communications

• Peripheral Buffering

• Line Printer Input Buffers

• Auto Dialers

• CRT Buffer Memories

• Radar Data Acquisition

CD40105BMS is a low-power first-in-first-out (FIFO) “elastic”

storage register that can store 16 4-bit words. It is capable of

handling input and output data at different shifting rates. This

feature makes it particularly useful as a buffer between asyn-

chronous systems.

Each word position in the register is clocked by a control flip-

flop, which stores a marker bit. A “1” signifies that the posi-

tion’s data is filled and a “0” denotes a vacancy in that posi-

tion. The control flip-flop detects the state of the preceding

flip-flop and communicates its own status to the succeeding

flip-flop. When a control flip-flop is in the “0” state and sees a

“1” in the preceding flip-flop, it generates a clock pulse that

transfers data from the preceding four data latches into its

own four data latches and resets the preceding flip-flop to

“0”. The first and last control flip-flops have buffered outputs.

Since all empty locations “bubble” automatically to the input

end, and all valid data ripple through to the output end, the

status of the first control flip-flop (DATA-IN READY) indicates

if the FIFO is full, and the status of the last flip-flop (DATA-

OUT READY) indicates if the FIFO contains data. As the

earliest data are removed from the bottom of the data stack

(the output end), all data entered later will automatically

propagate (ripple) toward the output.

Loading Data - Data can be entered whenever the DATA-IN

READY (DIR) flag is high, by a low to high transition on the

SHIFT-IN (SI) input. This input must go low momentarily

before the next word is accepted by the FIFO. The DIR flag

will go low momentarily, until that data have been transferred

to the second location. The flag will remain low when all 16-

word locations are filled with valid data, and further pulses

on the SI input will be ignored until DIR goes high.

Continued on next page

Pinout

CD40105BMS

TOP VIEW

3 - STATE

CONTROL

1

DIR 2

16 VDD

15 SO

SI 3

14 DOR

D0 4

13 Q0

D1 5

12 Q1

D2 6

11 Q2

D3 7

10 Q3

VSS 8

9 MR

Functional Diagram

3-STATE

CONTROL

D0

D1

D2

D3

SHIFT IN

SHIFT OUT

4

5

6

7

3

15

1

MASTER

RESET

9

13 Q0

12 Q1

11 Q2

10

Q3

14 DATA-OUT

READY

2 DATA-IN

READY

VDD = 16

VSS = 8

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

7-1317

File Number 3353

1 page

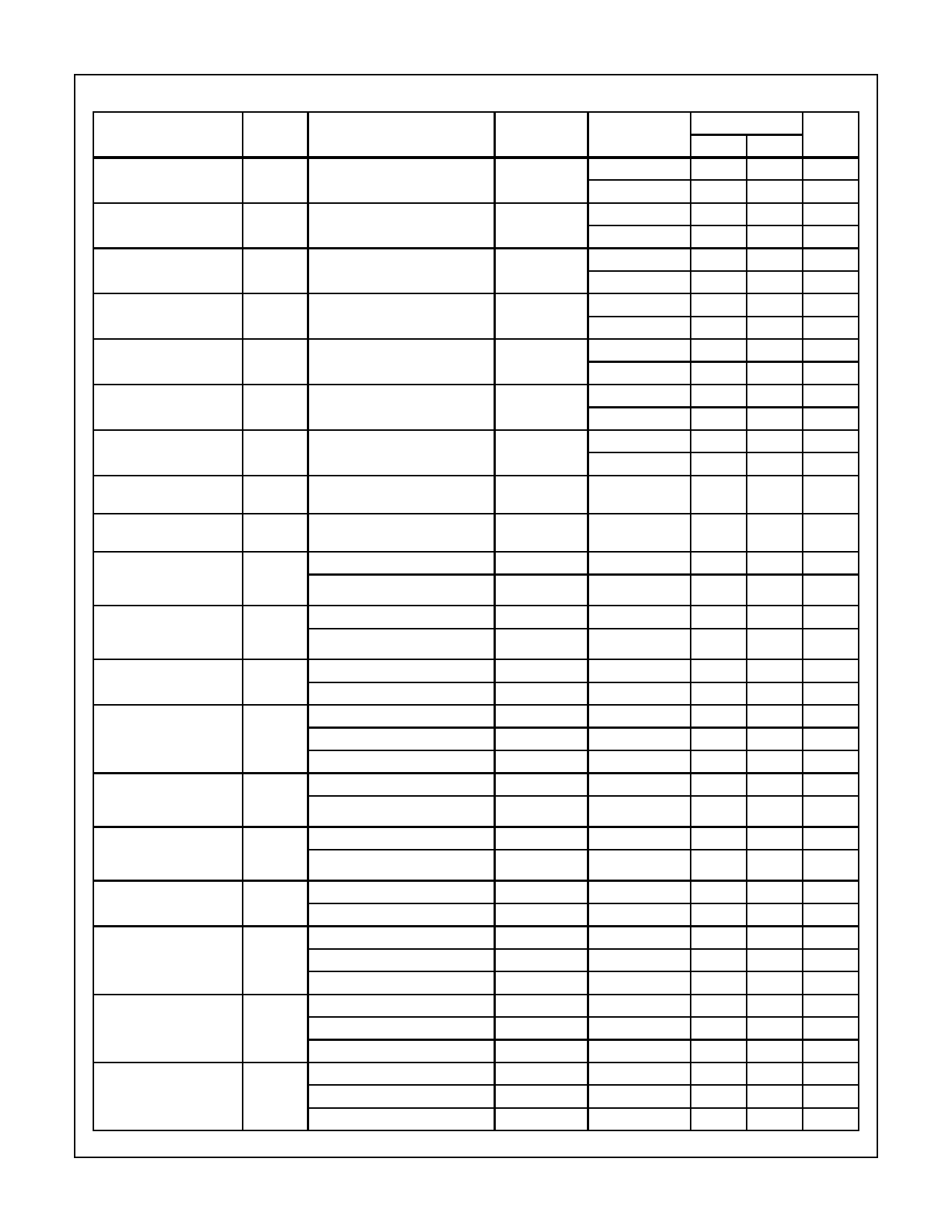

Specifications CD40105BMS

TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS (Continued)

LIMITS

PARAMETER

Output Current (Sink)

SYMBOL

CONDITIONS

IOL5 VDD = 5V, VOUT = 0.4V

Output Current (Sink)

IOL10 VDD = 10V, VOUT = 0.5V

Output Current (Sink)

IOL15 VDD = 15V, VOUT = 1.5V

Output Current (Source) IOH5A VDD = 5V, VOUT = 4.6V

Output Current (Source) IOH5B VDD = 5V, VOUT = 2.5V

Output Current (Source) IOH10 VDD = 10V, VOUT = 9.5V

Output Current (Source) IOH15 VDD =15V, VOUT = 13.5V

Input Voltage Low

VIL VDD = 10V, VOH > 9V, VOL < 1V

Input Voltage High

VIH VDD = 10V, VOH > 9V, VOL < 1V

Propagation Delay

Shift or Reset to Data Out

Ready

Propagation Delay Ripple

through Delay Input to

Output

Propagation Delay

Shift-In to Data-In Ready

Propagation Delay

Shift Out to QN Out

Propagation Delay

3-State Control to Data

Out

Propagation Delay

3-State Control to Data

Out

Maximum Shift-In or

Shift-Out Rate

Maximum Shift-In or

Shift-Out Rise Time

Maximum Shift-In Fall

Time

Maximum Shift-Out Fall

Time

TPHL1

TPLH3

TPHL2

TPHL4

TPLH4

TPZH

TPZL

TTHZ

TPLZ

FCL

TR

TF

TF

VDD = 10V

VDD = 15V

VDD = 10V

VDD = 15V

VDD = 10V

VDD = 15V

VDD = 5V

VDD = 10V

VDD = 15V

VDD = 10V

VDD = 15V

VDD = 10V

VDD = 15V

VDD = 10V

VDD = 15V

VDD = 5V

VDD = 10V

VDD = 15V

VDD = 5V

VDD = 10V

VDD = 15V

VDD = 5V

VDD = 10V

VDD = 15V

NOTES

1, 2

1, 2

1, 2

1, 2

1, 2

1, 2

1, 2

1, 2

1, 2

1, 2, 3

1, 2, 3

1, 2, 3

1, 2, 3

1, 2, 3

1, 2, 3

1, 2, 3

1, 2, 3

1, 2, 3

1, 2, 4

1, 2, 4

1, 2, 3

1, 2, 3

1, 2

1, 2

3

3

3

3

3

3

3

3

3

TEMPERATURE

+125oC

-55oC

+125oC

-55oC

+125oC

-55oC

+125oC

-55oC

+125oC

-55oC

+125oC

-55oC

+125oC

-55oC

+25oC, +125oC,

-55oC

+25oC, +125oC,

-55oC

+25oC

+25oC

+25oC

+25oC

+25oC

+25oC

+25oC

+25oC

+25oC

+25oC

+25oC

+25oC

+25oC

+25oC

+25oC

+25oC

+25oC

+25oC

+25oC

+25oC

+25oC

+25oC

+25oC

+25oC

MIN

0.36

0.64

0.9

1.6

2.4

4.2

-

-

-

-

-

-

-

-

-

7

-

-

-

-

-

-

-

-

-

-

-

-

-

3

4

-

-

-

-

-

-

-

-

-

MAX

-

-

-

-

-

-

-0.36

-0.64

-1.15

-2.0

-0.9

-1.6

-2.4

-4.2

3

-

180

130

2

1.4

130

90

420

380

250

120

80

100

80

-

-

15

15

15

15

15

15

15

5

5

UNITS

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

V

V

ns

ns

µs

µs

ns

ns

ns

ns

ns

ns

ns

ns

ns

MHz

MHz

µs

µs

µs

µs

µs

µs

µs

µs

µs

7-1321

5 Page | ||

| Páginas | Total 10 Páginas | |

| PDF Descargar | [ Datasheet CD40105BMS.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CD40105BMS | CMOS FIFO Register | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |