|

|

PDF EM68C16CWQE Data sheet ( Hoja de datos )

| Número de pieza | EM68C16CWQE | |

| Descripción | 64M x 16 bit DDRII Synchronous DRAM | |

| Fabricantes | Etron Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de EM68C16CWQE (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

EtronTech

EM68C16CWQE

64M x 16 bit DDRII Synchronous DRAM (SDRAM)

Advance (Rev. 1.6, May /2016)

Features

JEDEC Standard Compliant

JEDEC standard 1.8V I/O (SSTL_18-compatible)

Power supplies: VDD & VDDQ = +1.8V 0.1V

Operating temperature: TC = 0~85°C

Supports JEDEC clock jitter specification

Fully synchronous operation

Fast clock rate: 333/400/533 MHz

Differential Clock, CK & CK#

Bidirectional single/differential data strobe

- DQS & DQS#

8 internal banks for concurrent operation

4-bit prefetch architecture

Internal pipeline architecture

Precharge & active power down

Programmable Mode & Extended Mode registers

Posted CAS# additive latency (AL): 0, 1, 2, 3, 4, 5, 6

WRITE latency = READ latency - 1 tCK

Burst lengths: 4 or 8

Burst type: Sequential / Interleave

DLL enable/disable

Off-Chip Driver (OCD)

- Impedance Adjustment

- Adjustable data-output drive strength

On-die termination (ODT)

RoHS compliant

Auto Refresh and Self Refresh

8192 refresh cycles / 64ms

84-ball 8 x 12.5 x 1.2mm (max) FBGA package

- Pb and Halogen Free

Overview

The EM68C16C is a high-speed CMOS Double-

Data-Rate-Two (DDR2), synchronous dynamic random

- access memory (SDRAM) containing 1024 Mbits in a

16-bit wide data I/Os. It is internally configured as a 8-

bank DRAM, 8 banks x 8Mb addresses x 16 I/Os. The

device is designed to comply with DDR2 DRAM key

features such as posted CAS# with additive latency,

Write latency = Read latency -1, Off-Chip Driver (OCD)

impedance adjustment, and On Die Termination(ODT).

All of the control and address inputs are synchronized

with a pair of externally supplied differential clocks.

Inputs are latched at the cross point of differential clocks

(CK rising and CK# falling). All I/Os are synchronized

with a pair of bidirectional strobes (DQS and DQS#) in

a source synchronous fashion. The address bus is used

to convey row, column, and bank address information

in RAS #, CAS# multiplexing style. Accesses begin with

the registration of a Bank Activate command, and then

it is followed by a Read or Write command. Read and

write accesses to the DDR2 SDRAM are 4 or 8-bit burst

oriented; accesses start at a selected location and

continue for a programmed number of locations in a

programmed sequence. Operating the eight memory

banks in an interleaved fashion allows random access

operation to occur at a higher rate than is possible with

standard DRAMs. An auto precharge function may be

enabled to provide a self-timed row precharge that is

initiated at the end of the burst sequence. A sequential

and gapless data rate is possible depending on burst

length, CAS latency, and speed grade of the device.

Table 1. Ordering Information

Part Number

Clock Frequency Data Rate

EM68C16CWQE-18H

533MHz

1066Mbps/pin

EM68C16CWQE-25H

400MHz

800Mbps/pin

EM68C16CWQE-3H

333MHz

667Mbps/pin

WQ: indicates 8 x 12.5 x 1.2mm FBGA Package

E: indicates Generation Code

H: indicates Pb and Halogen Free

Power Supply

VDD 1.8V, VDDQ 1.8V

VDD 1.8V, VDDQ 1.8V

VDD 1.8V, VDDQ 1.8V

Package

FBGA

FBGA

FBGA

Etron Technology, Inc.

No. 6, Technology Rd. V, Hsinchu Science Park, Hsinchu, Taiwan 30078, R.O.C.

TEL: (886)-3-5782345 FAX: (886)-3-5778671

Etron Technology, Inc. reserves the right to change products or specification without notice.

1 page

EtronTech

EM68C16CWQE

Ball Descriptions

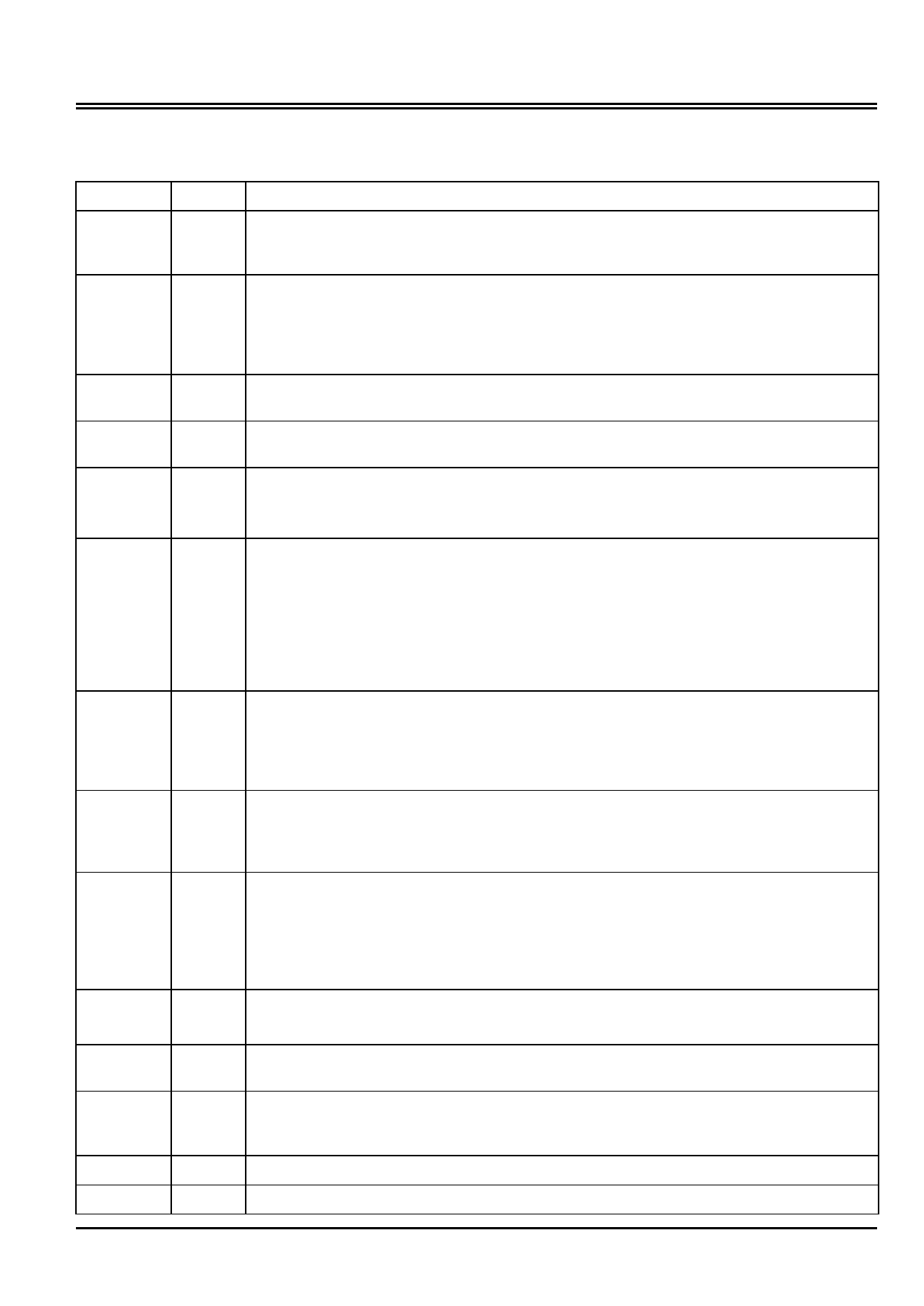

Table 3. Ball Descriptions

Symbol Type

Description

CK, CK#

Input

Differential Clock: CK, CK# are driven by the system clock. All SDRAM input signals are

sampled on the crossing of positive edge of CK and negative edge of CK#. Output (Read)

data is referenced to the crossings of CK and CK# (both directions of crossing).

CKE

Input

Clock Enable: CKE activates (HIGH) and deactivates (LOW) the CK signal. If CKE goes

LOW synchronously with clock, the internal clock is suspended from the next clock cycle

and the state of output and burst address is frozen as long as the CKE remains LOW.

When all banks are in the idle state, deactivating the clock controls the entry to the Power

Down and Self Refresh modes.

BA0-BA2

Input Bank Address: BA0-BA2 define to which bank the BankActivate, Read, Write, or Bank

Precharge command is being applied.

A0-A12

Input Address Inputs: A0-A12 are sampled during the BankActivate command (row address A0-

A12) and Read/Write command (column address A0-A9 with A10 defining Auto Precharge).

CS# Input Chip Select: CS# enables (sampled LOW) and disables (sampled HIGH) the command

decoder. All commands are masked when CS# is sampled HIGH. CS# provides for external

bank selection on systems with multiple banks. It is considered part of the command code.

RAS#

Input

Row Address Strobe: The RAS# signal defines the operation commands in conjunction

with the CAS# and WE# signals and is latched at the crossing of positive edges of CK and

negative edge of CK#. When RAS# and CS# are asserted "LOW" and CAS# is asserted

"HIGH" either the BankActivate command or the Precharge command is selected by the

WE# signal. When the WE# is asserted "HIGH" the BankActivate command is selected and

the bank designated by BA is turned on to the active state. When the WE# is asserted

"LOW" the Precharge command is selected and the bank designated by BA is switched to

the idle state after the precharge operation.

CAS#

Input

Column Address Strobe: The CAS# signal defines the operation commands in

conjunction with the RAS# and WE# signals and is latched at the crossing of positive edges

of CK and negative edge of CK#. When RAS# is held "HIGH" and CS# is asserted "LOW"

the column access is started by asserting CAS# "LOW". Then, the Read or Write command

is selected by asserting WE# “HIGH" or “LOW".

WE#

Input

Write Enable: The WE# signal defines the operation commands in conjunction with the

RAS# and CAS# signals and is latched at the crossing of positive edges of CK and negative

edge of CK#. The WE# input is used to select the BankActivate or Precharge command

and Read or Write command.

LDQS,

LDQS#

UDQS

UDQS#

Input /

Output

Bidirectional Data Strobe: Specifies timing for Input and Output data. Read Data Strobe is

edge triggered. Write Data Strobe provides a setup and hold time for data and DQM. LDQS

is for DQ0~7, UDQS is for DQ8~15. The data strobes LDOS and UDQS may be used in

single ended mode or paired with LDQS# and UDQS# to provide differential pair signaling

to the system during both reads and writes.A control bit at EMR (1)[A10] enables or disables

all complementary data strobe signals.

LDM,

UDM

Input Data Input Mask: Input data is masked when DM is sampled HIGH during a write cycle.

LDM masks DQ0-DQ7, UDM masks DQ8-DQ15.

DQ0 - DQ15 Input / Data I/O: The Data bus input and output data are synchronized with positive and negative

Output edges of DQS/DQS#. The I/Os are byte-maskable during Writes.

ODT

Input

On Die Termination: ODT enables internal termination resistance. It is applied to each DQ,

LDQS/LDQS#, UDQS/UDQS#, LDM, and UDM signal. The ODT pin is ignored if the EMR

(1) is programmed to disable ODT.

VDD Supply Power Supply: +1.8V 0.1V

VSS Supply Ground

Rev. 1.6

5

May /2016

5 Page

EtronTech

EM68C16CWQE

EMR(2)

The extended mode register (2) controls refresh related features. The default value of the extended mode register (2)

is not defined, therefore the extended mode register (2) must be written after power-up for proper operation. The

extended mode register(2) is written by asserting LOW on CS#, RAS#, CAS#, WE#, HIGH on BA1 and LOW on

BA0, while controlling the states of address pins A0 ~ A12. The DDR2 SDRAM should be in all bank precharge with

CKE already HIGH prior to writing into the extended mode register (2). The mode register set command cycle time

(tMRD) must be satisfied to complete the write operation to the extended mode register (2). Mode register contents

can be changed using the same command and clock cycle requirements during normal operation as long as all

banks are in the precharge state.

Table 7. Extended Mode Register EMR(2) Bitmap

BA2 BA1 BA0 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 Address Field

0*5 1

0

0*1

SRF

0*1

DCC

PASR*3

Extended Mode Register(2)

A7 High Temperature Self-Refresh Rate Enable

0 Disable

1 Enable *2

BA1 BA0 MRS mode

00

MR

0 1 EMR(1)

1 0 EMR(2)

1 1 EMR(3)

A3 DCC Enable *4

0 Disable

1 Enable

A2 A1 A0 Partial Array Self Refresh for 4 Banks

0 0 0 Full array

0 0 1 Half Array (BA[1:0]=00&01)

0 1 0 Quarter Array (BA[1:0]=00)

0 1 1 Not defined

1 0 0 3/4 array (BA[1:0]=01,10&11)

1 0 1 Half array (BA[1:0]=10&11)

1 1 0 Quarter array (BA[1:0]=11)

1 1 1 Not defined

NOTE 1: The rest bits in EMRS(2) are reserved for future use and all bits in EMRS(2) except A0-A2, A7, BA0 and BA1 must

be programmed to 0 when setting the extended mode register(2) during initialization.

NOTE 2: Due to the migration nature, user needs to ensure the DRAM part supports higher than 85°C Tcase temperature

self-refresh entry. If the high temperature self-refresh mode is supported then controller can set the EMRS2[A7] bit

to enable the self-refresh rate in case of higher than 85°C temperature self-refresh operation.

NOTE 3: If PASR (Partial Array Self Refresh) is enabled, data located in areas of the array beyond the specified location will

be lost if self refresh is entered. Data integrity will be maintained if tREF conditions are met and no Self Refresh

command is issued.

NOTE 4: DCC (Duty Cycle Corrector) implemented, user may be given the controllability of DCC thru EMR (2) [A3] bit.

NOTE 5: BA2 is reserved for future use and must be set to 0 when programming the MR.

Rev. 1.6

11

May /2016

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet EM68C16CWQE.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| EM68C16CWQE | 64M x 16 bit DDRII Synchronous DRAM | Etron Technology |

| EM68C16CWQG | 64M x 16 bit DDRII Synchronous DRAM | Etron Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |