|

|

PDF CD40101BMS Data sheet ( Hoja de datos )

| Número de pieza | CD40101BMS | |

| Descripción | CMOS 9-Bit Parity Generator/Checker | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CD40101BMS (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

CD40101BMS

December 1992

CMOS 9-Bit Parity Generator/Checker

Features

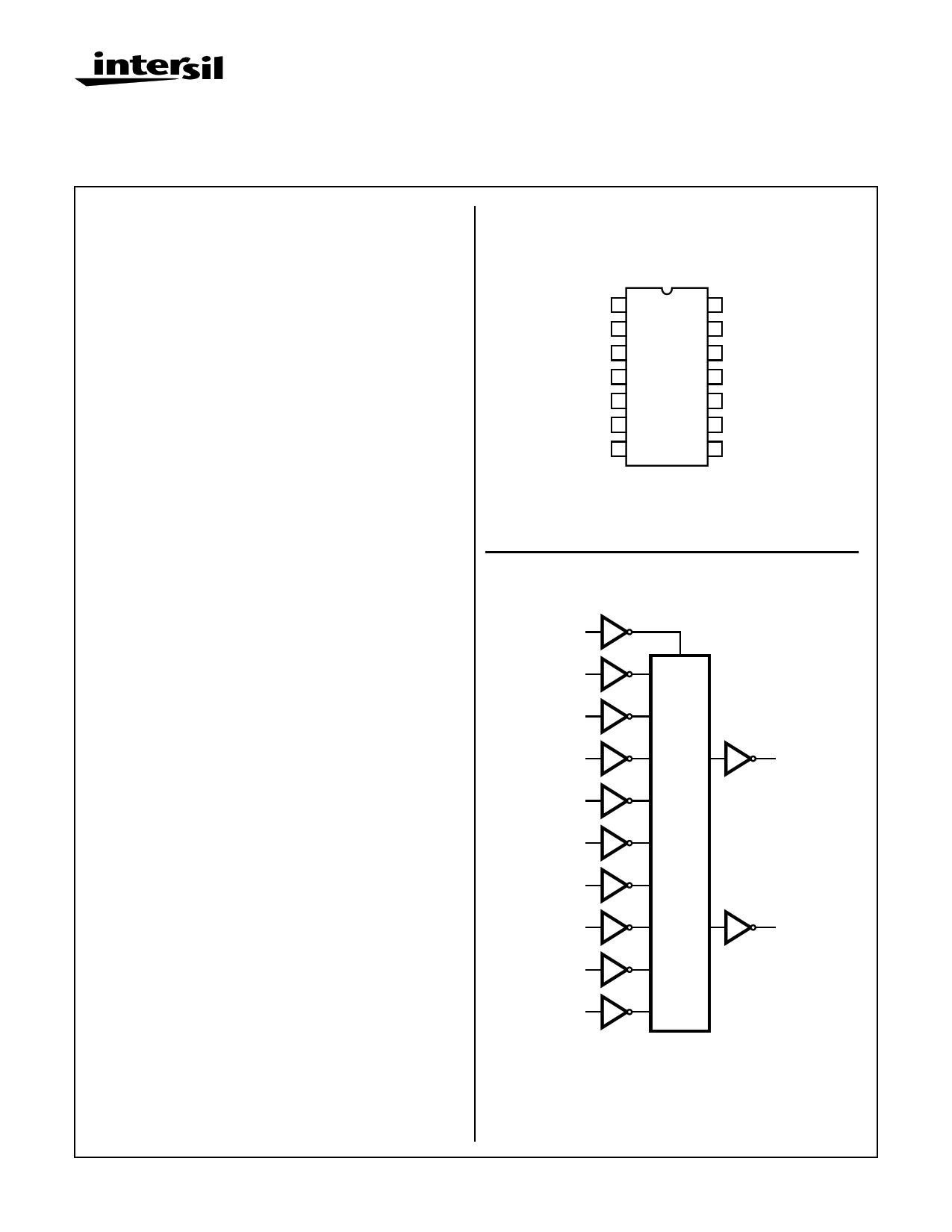

Pinout

• High Voltage Type (20V Rating)

• 100% Tested for Quiescent Current at 20V

CD40101BMS

TOP VIEW

• 5V, 10V and 15V Parametric Ratings

• Maximum Input Current of 1µA at 18V Over Full Pack-

age Temperature Range; 100nA at 18V and +25oC

• Noise Margin (Over Full Package/Temperature Range)

- 1V at VDD = 5V

- 2V at VDD = 10V

- 2.5V at VDD = 15V

• Standardized Symmetrical Output Characteristics

D1 1

D2 2

D3 3

D4 4

D9 5

ODD OUT 6

VSS 7

14 VDD

13 D8

12 D7

11 D6

10 D5

9 EVEN OUT

8 INHIBIT

• Meets All Requirements of JEDEC Tentative Standard

No. 13B, “Standard Specifications for Description of

‘B’ Series CMOS Devices”

Description

The CD40101BMS is a 9-bit (8 data bits plus 1 parity bit)

parity generator/checker. It may be used to detect errors in

data transmission or data retrieval. Odd and even outputs

facilitate odd or even parity generation and checking.

Functional Diagram

INHIBIT

8

When used as a parity generator, a parity bit is supplied

along with the data to generate an even or odd parity output.

D1 1

When used as a parity checker, the received data bits and

parity bits are compared for correct parity. The even or odd

outputs are used to indicate an error in the received data.

D2 2

Word length capability is expandable by cascading. The

CD40101BMS is also provided with an inhibit control. If the

inhibit control is set at logical “1”, the even and odd outputs

go to a logical “0”.

D3 3

D4 4

The CD40101BMS is supplied in these 14 lead outline

packages:

D5 10

DECODE

Braze Seal DIP

Frit Seal DIP

Ceramic Flatpack

H4H

H1B

H3W

D6 11

D7 12

VDD = 14

VSS = 7

EVEN

OUTPUT

9

ODD

OUTPUT

6

D8 13

D9 5

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

7-1286

File Number 3350

1 page

Specifications CD40101BMS

TABLE 6. APPLICABLE SUBGROUPS

CONFORMANCE GROUP

MIL-STD-883

METHOD

GROUP A SUBGROUPS

Interim Test 2 (Post Burn-In)

100% 5004

1, 7, 9

PDA (Note 1)

100% 5004

1, 7, 9, Deltas

Interim Test 3 (Post Burn-In)

100% 5004

1, 7, 9

PDA (Note 1)

100% 5004

1, 7, 9, Deltas

Final Test

100% 5004

2, 3, 8A, 8B, 10, 11

Group A

Sample 5005

1, 2, 3, 7, 8A, 8B, 9, 10, 11

Group B

Subgroup B-5

Sample 5005

1, 2, 3, 7, 8A, 8B, 9, 10, 11, Deltas

Subgroup B-6

Sample 5005

1, 7, 9

Group D

Sample 5005

1, 2, 3, 8A, 8B, 9

NOTE: 1. 5% Parameteric, 3% Functional; Cumulative for Static 1 and 2.

READ AND RECORD

IDD, IOL5, IOH5A

IDD, IOL5, IOH5A

Subgroups 1, 2, 3, 9, 10, 11

Subgroups 1, 2 3

CONFORMANCE GROUPS

Group E Subgroup 2

TABLE 7. TOTAL DOSE IRRADIATION

MIL-STD-883

METHOD

TEST

PRE-IRRAD

POST-IRRAD

5005

1, 7, 9

Table 4

READ AND RECORD

PRE-IRRAD

POST-IRRAD

1, 9 Table 4

TABLE 8. BURN-IN AND IRRADIATION TEST CONNECTIONS

OSCILLATOR

FUNCTION

OPEN

GROUND

VDD

9V ± -0.5V

50kHz

25kHz

Static Burn-In 1

Note 1

6, 9

1-5, 7, 8, 10-13

14

Static Burn-In 2

Note 1

6, 9

7 1-5, 8, 10-14

Dynamic Burn-

In Note 1

-

4, 7

12, 14

6, 9

2, 3, 5, 8, 10

1, 11, 13

Irradiation

Note 2

6, 9

7 1-5, 8, 10-14

NOTES:

1. Each pin except VDD and GND will have a series resistor of 10K ± 5%, VDD = 18V ± 0.5V

2. Each pin except VDD and GND will have a series resistor of 47K ± 5%; Group E, Subgroup 2, sample size is 4 dice/wafer, 0 failures,

VDD = 10V ± 0.5V

7-1290

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet CD40101BMS.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CD40101BMS | CMOS 9-Bit Parity Generator/Checker | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |