|

|

PDF EM63B165TS Data sheet ( Hoja de datos )

| Número de pieza | EM63B165TS | |

| Descripción | 32M x 16 bit Synchronous DRAM | |

| Fabricantes | Etron Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de EM63B165TS (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

EtronTech

EM63B165TS

32M x 16 bit Synchronous DRAM (SDRAM)

Advance (Rev. 2.0, Feb. /2016)

Features

Fast access time from clock: 4.5/5/5.4 ns

Fast clock rate: 200/166/143 MHz

Fully synchronous operation

Internal pipelined architecture

8M word x 16-bit x 4-bank

Programmable Mode registers

- CAS Latency: 2 or 3

- Burst Length: 1, 2, 4, 8, or full page

- Burst Type: Sequential or Interleaved

- Burst stop function

Auto Refresh and Self Refresh

8192 refresh cycles/64ms

CKE power down mode

Single +3.3V ±0.3V power supply

Operating Temperature: TA = 0~70°C

Interface: LVTTL

54-pin 400 mil plastic TSOP II package

- Pb free and Halogen free

Overview

The EM63B165 SDRAM is a high-speed CMOS

synchronous DRAM containing 512 Mbits. It is

internally configured as 4 Banks of 8M word x 16

DRAM with a synchronous interface (all signals

are registered on the positive edge of the clock

signal, CLK). Read and write accesses to the SDRAM

are burst oriented; accesses start at a selected

location and continue for a programmed number of

locations in a programmed sequence. Accesses

begin with the registration of a Bank Activate command

which is then followed by a Read or Write command.

The EM63B165 provides for programmable Read

or Write burst lengths of 1, 2, 4, 8, or full page, with

a burst termination option. An auto precharge function

may be enabled to provide a self-timed row precharge

that is initiated at the end of the burst sequence.

The refresh functions, either Auto or Self Refresh

are easy to use. By having a programmable mode

register, the system can choose the most suitable

modes to maximize its performance. These devices

are well suited for applications requiring high memory

bandwidth and particularly well suited to high

performance PC applications.

Table 1. Key Specifications

tCK3

tAC3

tRAS

tRC

EM63B165

Clock Cycle time(min.)

Access time from CLK (max.)

Row Active time(min.)

Row Cycle time(min.)

Table 2. Ordering Information

Part Number

Frequency

EM63B165TS-5SG

200MHz

EM63B165TS-6SG

166MHz

EM63B165TS-7SG

143MHz

TS: indicates TSOPII Package

S: indicates Stacked Dice

G: indicates Pb and Halogen Free

-5/6/7

5/6/7

4.5/5/5.4

40/42/42

55/60/63

ns

ns

ns

ns

Package

TSOP II

TSOP II

TSOP II

Etron Technology, Inc.

No. 6, Technology Rd. V, Hsinchu Science Park, Hsinchu, Taiwan 30078, R.O.C.

TEL: (886)-3-5782345 FAX: (886)-3-5778671

Etron Technology, Inc. reserves the right to change products or specification without notice.

1 page

EtronTech

EM63B165TS

DQ0-DQ15

NC

VDDQ

VSSQ

VDD

VSS

Input /

Output

-

Suply

Supply

Supply

Supply

Data I/O: The DQ0-15 input and output data are synchronized with the positive

edges of CLK. The I/Os are maskabled during Reads and Writes.

No Connect: These pins should be left unconnected.

DQ Power: Provide isolated power to DQs for improved noise immunity. (+3.3V 0.3V)

DQ Ground: Provide isolated ground to DQs for improved noise immunity. (0 V)

Power Supply: +3.3V 0.3V

Ground

Rev. 2.0

5 Feb. /2016

5 Page

EtronTech

EM63B165TS

CLK

COMMAND

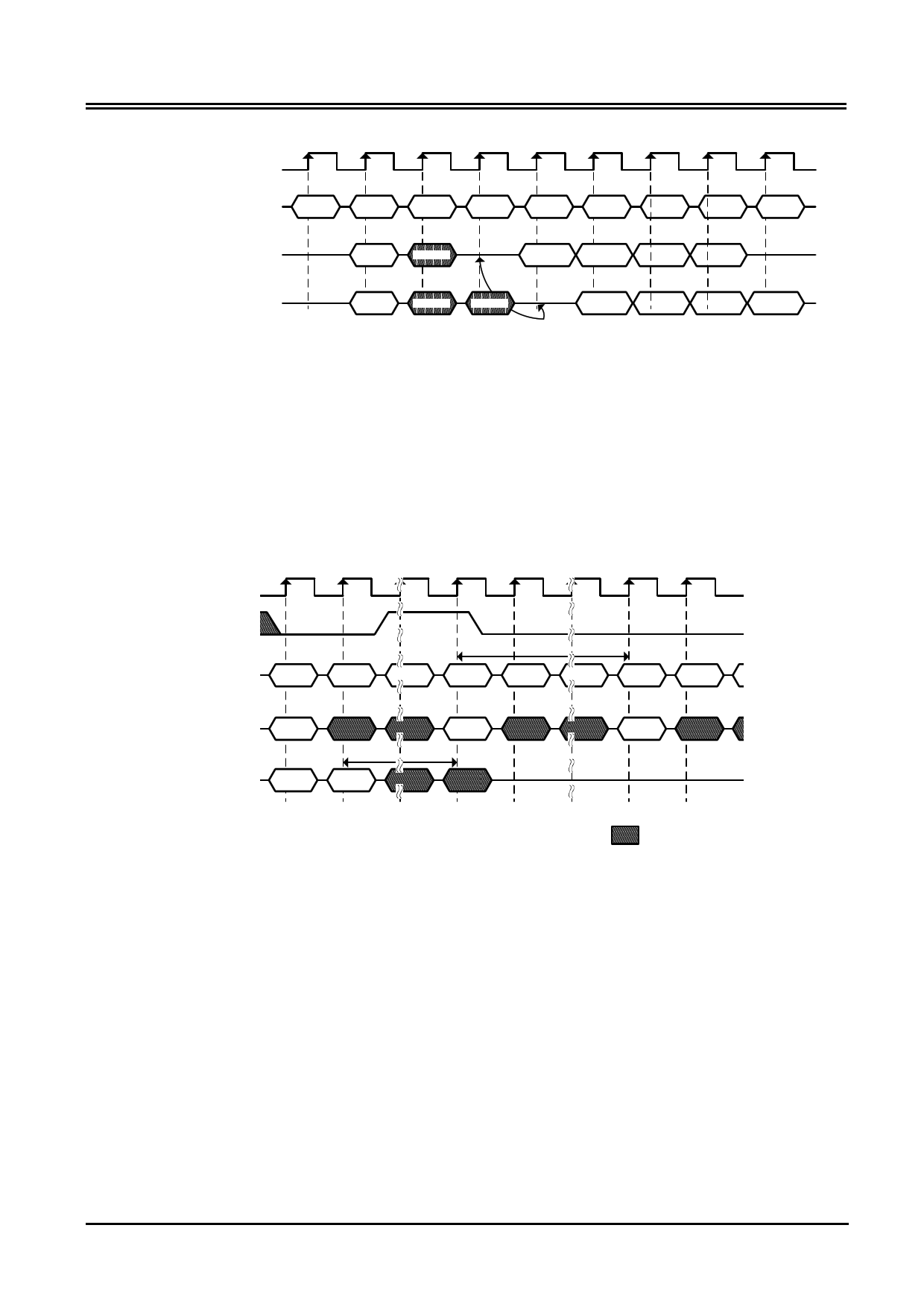

T0 T1 T2 T3 T4 T5 T6 T7 T8

NOP

WRITE A READ B

NOP

NOP

NOP

NOP

NOP

NOP

CAS# Latency=2

tCK2, DQ

DIN A0

don’t care

DOUT B0 DOUT B1 DOUT B2 DOUT B3

CAS# Latency=3

tCK3, DQ

DIN A0

don’t care

don’t care

DOUT B0 DOUT B1 DOUT B2 DOUT B3

Input data must be removed from the DQ at

least one clock cycle before the Read data

appears on the outputs to avoid data contention

Figure 12. Write Interrupted by a Read (Burst Length = 4, CAS# Latency = 2, 3)

The BankPrecharge/PrechargeAll command that interrupts a write burst without the auto

precharge function should be issued m cycles after the clock edge in which the last data-in element is

registered, where m equals tWR/tCK rounded up to the next whole number. In addition, the DQM signals

must be used to mask input data, starting with the clock edge following the last data-in element and

ending with the clock edge on which the BankPrecharge/PrechargeAll command is entered (refer to the

following figure).

CLK

DQM

COMMAND

T0 T1 T2 T3 T4 T5 T6 T7

WRITE

NOP

NOP

Precharge

tRP

NOP

NOP

Activate

NOP

ADDRESS

DQ

Bank

Col n

DIN

n

tWR

DIN

N+1

Bank (s)

ROW

Don’t Care

Note: The DQMs can remain low in this example if the length of the write burst is 1 or 2.

Figure 13. Write to Precharge

7 Write and AutoPrecharge command

(RAS# = "H", CAS# = "L", WE# = "L", BAs = Bank, A10 = "H", A0-A9 = Column Address)

The Write and AutoPrecharge command performs the precharge operation automatically after the

write operation. Once this command is given, any subsequent command can not occur within a time

delay of {(burst length -1) + tWR + tRP(min.)}. At full-page burst, only the write operation is performed in

this command and the auto precharge function is ignored.

Rev. 2.0

11 Feb. /2016

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet EM63B165TS.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| EM63B165TS | 32M x 16 bit Synchronous DRAM | Etron Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |