|

|

PDF CD4007UBMS Data sheet ( Hoja de datos )

| Número de pieza | CD4007UBMS | |

| Descripción | CMOS Dual Complementary Pair Plus Inverter | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CD4007UBMS (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

CD4007UBMS

November 1994

CMOS Dual Complementary Pair Plus Inverter

Features

Pinout

• High-Voltage Type (20V Rating)

• Standardized Symmetrical Output Characteristics

• Medium Speed Operation

- tPHL, tPLH = 30 ns (typ) at 10V

• 100% Tested for Maximum Quiescent Current at 20V

• Meets All Requirements of JEDEC Tentative Stan-

dards No. 13B, “Standard Specifications for Descrip-

tion of “B” Series CMOS Devices”

• Maximum Input Current of 1µA at 18V Over Full Pack-

age-Temperature Range; 100nA at 18V and +25oC

Applications

Q2 (P) DRAIN 1

Q2 (P) SOURCE 2

Q2 GATES 3

Q2 (N) SOURCE 4

Q2 (N) DRAIN 5

Q1 GATES 6

VSS, Q1, Q2, Q3 (N) 7

SUBSTRATES Q1 (N)

SOURCE

CD4007UBMS

TOP VIEW

14 VDD, Q1, Q2, Q3 (P)

SUBSTRATES, Q1(P) DRAIN

13 Q1 (P) SOURCE

12 Q3 (N) DRAIN, Q3 (P) SOURCE

11 Q3 (P) DRAIN

10 Q3 GATES

9 Q3 (N) SOURCE

8 Q1 (N) DRAIN

• Extremely High-Input Impedance Amplifiers

• Shapers

• Inverters

• Threshold Detector

• Linear Amplifiers

• Crystal Oscillators

Description

CD4007BMS types are comprised of three n-channel and

three p-channel enhancement-type MOS transistors. The

transistor elements are accessible through the package ter-

minals to provide a convenient means for constructing the

various typical circuits as shown in Figure 2.

More complex functions are possible using multiple pack-

ages. Numbers shown in parentheses indicate terminals that

are connected together to form the various configurations

listed.

The CD4007BMS is supplied in these 14 lead outline pack-

ages:

Functional Diagram

14 2

pp

11

p

6 133

1 10

12

85

nn

n

74

9

TERMINAL NO. 14 - VDD

TERMINAL NO. 7 - VSS

Braze Seal DIP H4Q

Frit Seal DIP

H1B

Ceramic Flatpack H3W

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

7-666

File Number 3291

1 page

Specifications CD4007UBMS

TABLE 6. APPLICABLE SUBGROUPS (Continued)

CONFORMANCE GROUP

MIL-STD-883

METHOD

GROUP A SUBGROUPS

Group D

Sample 5005

1, 2, 3, 8A, 8B, 9

NOTE: 1. 5% Parameteric, 3% Functional; Cumulative for Static 1 and 2.

READ AND RECORD

Subgroups 1, 2 3

CONFORMANCE GROUPS

Group E Subgroup 2

TABLE 7. TOTAL DOSE IRRADIATION

MIL-STD-883

METHOD

TEST

PRE-IRRAD

POST-IRRAD

5005

1, 7, 9

Table 4

READ AND RECORD

PRE-IRRAD

POST-IRRAD

1, 9 Table 4

TABLE 8. BURN-IN AND IRRADIATION TEST CONNECTIONS

OSCILLATOR

FUNCTION

OPEN

GROUND

VDD

9V ± -0.5V

50kHz

25kHz

Static Burn-In

1 Note 1

1, 5, 8, 12, 13

3, 4, 6, 7, 9, 10

2, 11, 14

Static Burn-In

2 Note 1

1, 5, 8, 12, 13

4, 7, 9

2, 3, 6, 10, 11, 14

Dynamic Burn-

In Note 1

-

4, 7, 9

2, 11, 14

1, 5, 8, 12, 13

3, 6, 10

-

Irradiation

Note 2

1, 5, 8, 12, 13

4, 7, 9

2, 3, 6, 10, 11, 14

NOTE:

1. Each pin except VDD and GND will have a series resistor of 10K ±5%, VDD = 18V ±0.5V

2. Each pin except VDD and GND will have a series resistor of 47K ± 5%; Group E, Subgroup 2, sample size is 4 dice/wafer, 0 failures, VDD

= 10V ±0.5V

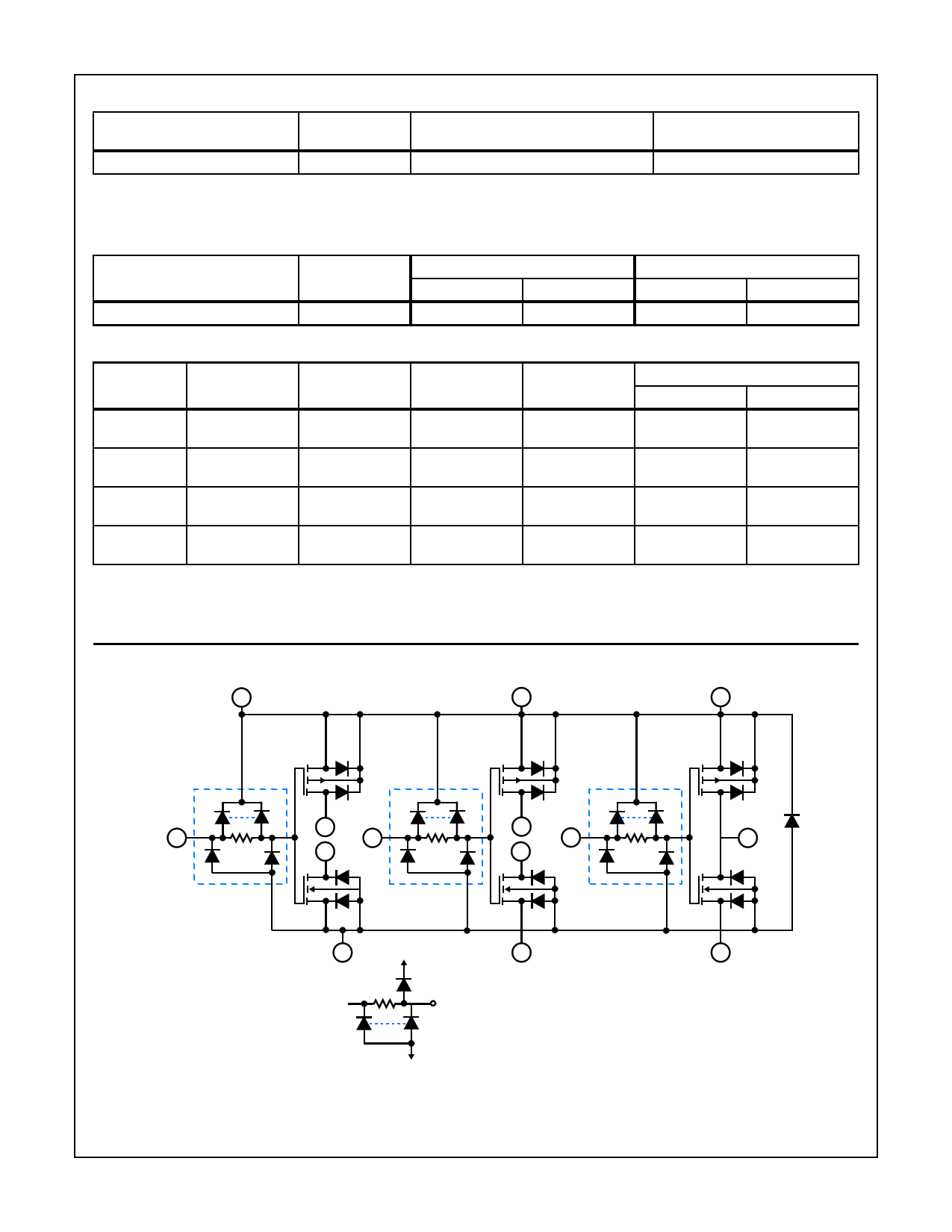

Schematic Diagram

14

2 **

11 **

D2 D2

D2

* D2 * D2 *

D2

6

R1 D2 ** 13

D2

Q1 3

R1 D2 ** 1

D2

Q2 10

R1 D2

D1 D1

8

D1

D1 D1

5

D1

D1 D1

D2

12 Q3

D1 **

D1

*CMOS INPUT

PROTECTION

D1

D1

D1

NETWORK

**CMOS OUTPUT PROTECTION

NETWORK BETWEEN TERMINAL

NOS. 1, 2, 4, 5, 8, 9, 11, 12, 13

AND THE CORRESPONDING

DRAINS AND/OR SOURCES

7 VDD

4 ** PARASITIC AND

9 **

NETWORK COMPONENTS

D1 = N+ TO P WELL

R2

D2

OUTPUT

TERMINAL

D2 = P+ TO SUBSTRATE

R1 = 1 - 5 KΩ

R2 = 15 - 30Ω

D1 D1

VSS

FIGURE 1. DETAILED SCHEMATIC DIAGRAM OF CD4007UBMS SHOWING INPUT, OUTPUT, AND PARASITIC DIODES

7-670

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet CD4007UBMS.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CD4007UBMS | CMOS Dual Complementary Pair Plus Inverter | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |