|

|

PDF ICS9FG104D Data sheet ( Hoja de datos )

| Número de pieza | ICS9FG104D | |

| Descripción | Frequency Generator | |

| Fabricantes | IDT | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICS9FG104D (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

DATASHEET

Frequency Generator for CPU, QPI, FBD, PCIe Gen 2 & SATA

ICS9FG104D

Description

The ICS9FG104D is a Frequency Timing Generator that provides 4

differential output pairs that are compliant to the Intel CK410

specification. It also provides support for PCI-Express and SATA.

The part synthesizes several output frequencies from either a

14.31818 Mhz crystal or a 25 MHz crystal. The device can also be

driven by a reference input clock instead of a crystal. It provides

outputs with cycle-to-cycle jitter of less than 50 ps and output-to-

output skew of less than 35 ps. The ICS9FG104D also provides a

copy of the reference clock. Frequency selection can be

accomplished via strap pins or SMBus control.

Key Specifications

Features/Benefits

• Generates common frequencies from 14.318 MHz or

25 MHz

• Crystal or reference input

• 4 - 0.7V current-mode differential output pairs

• Supports Serial-ATA at 100 MHz

• Two spread spectrum modes: 0 to -0.5 downspread

and +/-0.25% centerspread

• Unused inputs may be disabled in either driven or Hi-Z

state for power management.

• Output cycle-to-cycle jitter < 50 ps

• Output to output skew < 35 ps

• +/-300 ppm frequency accuracy on output clocks

• +/-50 ppm at any frequency w/spread off

Functional Block Diagram

XIN/CLKIN

X2

2

OSC

PROGRAMMABLE

SPREAD PLL

STOP

LOGIC

4

REFOUT

DIF(3:0)

SPREAD

SEL14M_25M#

DIF_STOP#

FS(2:0)

SDATA

SCLK

CONTROL

LOGIC

IREF

IDT® Frequency Generator for CPU, QPI, FBD, PCIe Gen 2 & SATA

1

1541C—12/16/10

1 page

ICS9FG104D

Frequency Generator for CPU, QPI, FBD, PCIe Gen 2 & SATA

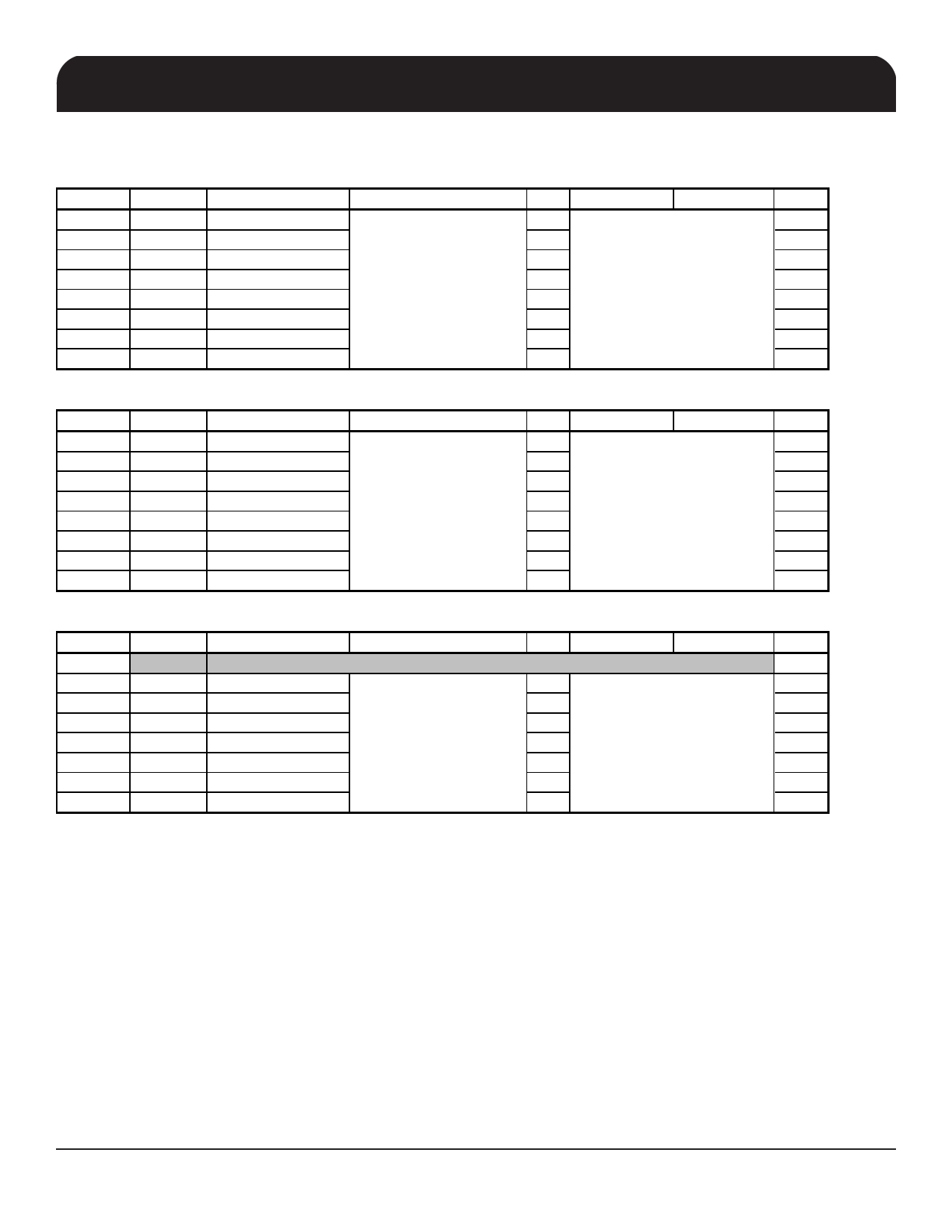

Electrical Characteristics - DIF 0.7V Current Mode Differential Pair

TA = TAM BIENT; VDD = 3.3 V +/-5%; CL =2pF, RS=33.2Ω, RP=49.9Ω, IREF = 475Ω

PARAMETER

SYMBOL

CONDITIONS

MIN TYP MAX UNITS NOTES

Output Impedance

Zo1

VO = Vx

3000

Ω1

Voltage High

Voltage Low

VHigh

VLow

Statistical measurement on

single ended signal using

oscilloscope math function.

660

-150

850

mV

150

1

1

Max Voltage

Min Voltage

Crossing Voltage (abs)

Vovs

Vuds

Vcross(abs)

Measurement on single ended

signal using absolute value.

-300

250

1150

550

mV

mV

1

1

1

Crossing Voltage (var)

d-Vcross Crossing variation over all edges

140 mV

1

Long Accuracy

ppm

see Tperiod min-max values

-300

300 ppm

400MHz nominal

2.49988 2.5000 2.5001 ns

400MHz spread

2.4993

2.5133 ns

333.33MHz nominal

2.99985 3.0000 3.0002 ns

333.33MHz spread

2.9991

3.016

ns

266.66MHz nominal

3.74981 3.7500 3.7502 ns

266.66MHz spread

3.7489

3.77 ns

Average period

Tperiod

200MHz nominal

200MHz spread

4.9998 5.0000 5.0003

4.9985

5.0266

ns

ns

166.66MHz nominal

5.9997 6.0000 6.0003 ns

166.66MHz spread

5.9982

6.0320 ns

133.33MHz nominal

7.4996 7.5000 7.5004 ns

133.33MHz spread

7.4978

5.4000 ns

100.00MHz nominal

9.9995 10.0000 10.0005 ns

100.00MHz spread

9.9970

10.0533 ns

400MHz nominal/spread

2.4143

ns

333.33MHz nominal/spread 2.9141

ns

266.66MHz nominal/spread 3.6639

ns

Absolute min period

Tabsmin

200MHz nominal/spread

4.8735

ns

166.66MHz nominal/spread 5.8732

ns

133.33MHz nominal/spread 7.3728

ns

100.00MHz nominal/spread 9.8720

ns

Rise Time

tr

VOL = 0.175V, VOH = 0.525V

175

700 ps

Fall Time

tf

VOH = 0.525V VOL = 0.175V

175

700 ps

Rise Time Variation

d-tr

125 ps

Fall Time Variation

d-tf

125 ps

Duty Cycle

dt3

Measured Differentially

45

55 %

Skew, output to output

tsk3

VT = 50%

35 ps

Jitter, Cycle to cycle

tjcyc-cyc

Measured Differentially

50 ps

1Guaranteed by design and characterization, not 100% tested in production.

2 All Long Term Accuracy and Clock Period specifications are guaranteed assuming that REFOUT is tuned to 0

3 Figures are for down spread.

4 This figure is the peak-to-peak phase jitter as defined by PCI-SIG for a PCI Express reference clock. Please visit

http://www.pcisig.com for additional details

5 +/- 50 ppm at any frequency with spread off

1,2,5

2

2,3

2

2,3

2

2,3

2

2,3

2

2,3

2

2,3

2

2,3

1,2

1,2

1,2

1,2

1,2

1,2

1,2

1

1

1

1

1

1

1

IDT® Frequency Generator for CPU, QPI, FBD, PCIe Gen 2 & SATA

1541C—12/16/10

5

5 Page

ICS9FG104D

Frequency Generator for CPU, QPI, FBD, PCIe Gen 2 & SATA

SMBus Table: PLL Frequency Control Register

Byte 11

Pin #

Name

Control Function

Bit 7

-

PLL N Div7

Bit 6

-

PLL N Div6

Bit 5

Bit 4

Bit 3

Bit 2

-

-

-

-

PLL N Div5

PLL N Div4

PLL N Div3

PLL N Div2

N Divider Programming

Byte11 bit(7:0) and Byte10

bit(7:6)

Bit 1

-

PLL N Div1

Bit 0

-

PLL N Div0

Type

0

1 Default

RW X

RW The decimal representation of M

RW and N Divider in Byte 11 and 12 will

RW configure the PLL VCO frequency.

Default at power up = latch-in or

RW Byte 0 Rom table. VCO Frequency

RW = fXTAL x [NDiv(9:0)+8] /

RW [MDiv(5:0)+2]

X

X

X

X

X

X

RW X

SMBus Table: PLL Spread Spectrum Control Register

Byte 12

Pin #

Name

Control Function

Bit 7

-

PLL SSP7

Bit 6

-

PLL SSP6

Bit 5

-

PLL SSP5

Bit 4

Bit 3

-

-

PLL SSP4

PLL SSP3

Spread Spectrum

Programming bit(7:0)

Bit 2

-

PLL SSP2

Bit 1

-

PLL SSP1

Bit 0

-

PLL SSP0

Type

RW

RW

RW

RW

RW

RW

RW

RW

01

These Spread Spectrum bits in

Byte 13 and 14 will program the

spread pecentage of PLL

Default

X

X

X

X

X

X

X

X

SMBus Table: PLL Spread Spectrum Control Register

Byte 13

Pin #

Name

Control Function

Bit 7

-

Reserved

Bit 6

-

PLL SSP14

Bit 5

-

PLL SSP13

Bit 4

Bit 3

Bit 2

-

-

-

PLL SSP12

PLL SSP11

PLL SSP10

Spread Spectrum

Programming bit(14:8)

Bit 1

-

PLL SSP9

Bit 0

-

PLL SSP8

Type

RW

RW

RW

RW

RW

RW

RW

01

These Spread Spectrum bits in

Byte 13 and 14 will program the

spread pecentage of PLL

Default

0

X

X

X

X

X

X

X

IDT® Frequency Generator for CPU, QPI, FBD, PCIe Gen 2 & SATA

11

1541C—12/16/10

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet ICS9FG104D.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICS9FG104 | Programmable FTG for Differential P4TM CPU | Integrated Circuit Systems |

| ICS9FG104 | Frequency Generator | Integrated Device Technology |

| ICS9FG104D | Frequency Generator | IDT |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |