|

|

PDF DM9332 Data sheet ( Hoja de datos )

| Número de pieza | DM9332 | |

| Descripción | 10/100Mbps Ethernet Fiber/Twisted Pair Single Chip Media Converter | |

| Fabricantes | DAVICOM | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de DM9332 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

DAVICOM Semiconductor, Inc.

DM9332

10/100Mbps Ethernet Fiber/Twisted Pair

Single Chip Media Converter

DATA SHEET

Preliminary

Version: DM9332-DS-P01

March 5, 2012

1 page

DM9332

10/100Mbps Ethernet Fiber/Twisted Pair Single Chip Media Converter

8.14 DAVICOM Specified Disconnect Counter Register (DISCR) – 17H ........................................................ 42

8.15 Power Saving Control Register (PSCR) – 1DH ......................................................................................... 42

9. FUNCTIONAL DESCRIPTION....................................................................................... 43

9.1 Serial Management Interface........................................................................................................................ 43

9.2 Switch function:............................................................................................................................................. 44

9.2.1 Address Learning ..................................................................................................................................... 44

9.2.2 Address Aging .......................................................................................................................................... 44

9.2.3 Packet Forwarding ................................................................................................................................... 44

9.2.4 Inter-Packet Gap (IPG) ............................................................................................................................ 44

9.2.5 Back-off Algorithm.................................................................................................................................... 44

9.2.6 Late Collision............................................................................................................................................ 44

9.2.7 Full Duplex Flow Control .......................................................................................................................... 44

9.2.8 Half Duplex Flow Control ......................................................................................................................... 44

9.2.9 Partition Mode .......................................................................................................................................... 45

9.2.10 Broadcast Storm Filtering....................................................................................................................... 45

9.2.11 Bandwidth Control.................................................................................................................................. 45

9.2.12 Port Monitoring Support ......................................................................................................................... 45

9.2.13 VLAN Support ........................................................................................................................................ 46

9.2.13.1 Port-Based VLAN................................................................................................................................ 46

9.2.13.2 802.1Q-Based VLAN........................................................................................................................... 46

9.2.13.3 Tag/Untag ........................................................................................................................................... 46

9.2.14 Priority Support ...................................................................................................................................... 47

9.2.14.1 Port-Based Priority .............................................................................................................................. 47

9.2.14.2 802.1p-Based Priority.......................................................................................................................... 47

9.2.14.3 DiffServ-Based Priority........................................................................................................................ 47

9.3 MII Interface.................................................................................................................................................... 48

9.3.1 MII data interface ..................................................................................................................................... 48

9.3.2 MII Serial Management ............................................................................................................................ 48

9.3.3 Serial Management Interface ................................................................................................................... 49

9.3.4 Management Interface - Read Frame Structure ...................................................................................... 49

Preliminary datasheet

DM9332-15-DS-P01

March 5, 2012

5

5 Page

DM9332

10/100Mbps Ethernet Fiber/Twisted Pair Single Chip Media Converter

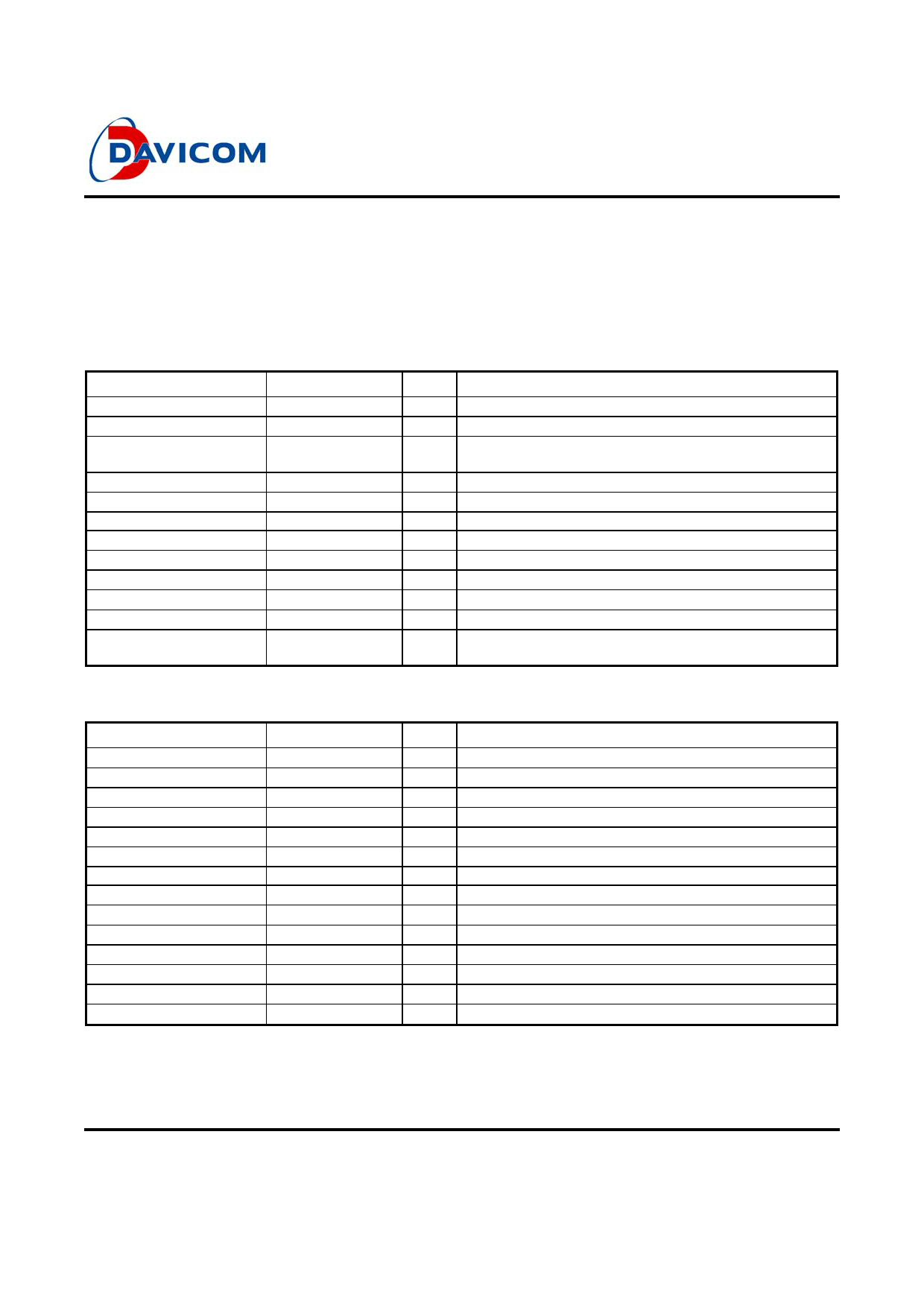

5. Pin Description

I = Input, O = Output, I/O = Input / Output, O/D = Open Drain, P = Power, PD=internal pull-low (about 50K Ohm)

# = asserted Low

5.1 P2 MII / RMII / Reverse MII Interfaces

5.1.1 MII Interfaces

Pin No.

2

3

5,6,7,9

10

12

14

15

17

18

19

20

21,22,24,25

Pin Name

MDC

MDIO

TXD2_3~0

TXE2

TXC2

TXER2

CRS2

COL2

RXER2

RXC2

RXDV2

RXD2_3~0

I/O

O,PD

I/O

O,PD

O,PD

I/O

O,PD

I/O

I/O

I

I

I

I

Description

MII Serial Management Data Clock

MII Serial Management Data

Port 2 MII Transmit Data

4-bit nibble data outputs (synchronous to the TXC2)

Port 2 MII Transmit Enable

Port 2 MII Transmit Clock.

Port 2 MII Transmit Error

Port 2 MII Carrier Sense

Port 2 MII Collision Detect.

Port 2 MII Receive Error

Port 2 MII Receive Clock

Port 2 MII Receive Data Valid

Port 2 MII Receive Data

4-bit nibble data input (synchronous to RXC2)

5.1.2 RMII Interfaces

Pin No.

2

3

5,6

7,9

10

12

14

15

17

18

19

20

21,22

24,25

Pin Name

MDC

MDIO

TXD2_3~2

TXD2_1~0

TXE2

TXC2

TXER2

CRS2

COL2

RXER2

RXC2

RXDV2

RXD2_3~2

RXD2_1~0

I/O

O,PD

I/O

O,PD

O,PD

O,PD

O

O

I

I

I

I

I

I

I

Description

MII Serial Management Data Clock

MII Serial Management Data

Reserved

RMII Transmit Data

RMII Transmit Enable.

Reserved

Port 2 MII Transmit Error

RMII CRS_DV

Reserved, tie to ground in application.

Reserved, tie to ground in application.

50MHz reference clock.

Reserved, tie to ground in application.

Reserved, tie to ground in application.

RMII Receive Data.

Preliminary datasheet

DM9332-15-DS-P01

March 5, 2012

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet DM9332.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DM9331A | 100 Mbps Twisted Pair/Fiber Ethernet Media Converter Chip | DAVICOM |

| DM9332 | 10/100Mbps Ethernet Fiber/Twisted Pair Single Chip Media Converter | DAVICOM |

| DM9334 | 9334/DM9334 8-Bit Addressable Latch (Rev. A) | Texas Instruments |

| DM9338 | 9338/DM9338 8-Bit Multiple Port Register (Rev. A) | Texas Instruments |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |