|

|

PDF HY57V161610ET-10I Data sheet ( Hoja de datos )

| Número de pieza | HY57V161610ET-10I | |

| Descripción | 2 Banks x 512K x 16 Bit Synchronous DRAM | |

| Fabricantes | Hynix Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de HY57V161610ET-10I (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

HY57V161610ET-I

2 Banks x 512K x 16 Bit Synchronous DRAM

DESCRIPTION

THE Hynix HY57V161610E is a 16,777,216-bits CMOS Synchronous DRAM, ideally suited for the main memory and graphic appli-

cations which require large memory density and high bandwidth. HY57V161610E is organized as 2banks of 524,288x16.

HY57V161610E is offering fully synchronous operation referenced to a positive edge clock. All inputs and outputs are synchronized

with the rising edge of the clock input. The data paths are internally pipelined to achieve very high bandwidth. All input and output

voltage levels are compatible with LVTTL.

Programmable options include the length of pipeline (Read latency of 1,2 or 3), the number of consecutive read or write cycles initi-

ated by a single control command (Burst length of 1,2,4,8 or full page), and the burst count sequence(sequential or interleave). A

burst of read or write cycles in progress can be terminated by a burst terminate command or can be interrupted and replaced by a

new burst read or write command on any cycle. (This pipeline design is not restricted by a `2N` rule.)

FEATURES

• Single 3.0V to 3.6V power supply

• All device pins are compatible with LVTTL interface

• JEDEC standard 400mil 50pin TSOP-II with 0.8mm of pin

pitch

• All inputs and outputs referenced to positive edge of system

clock

• Data mask function by UDQM/LDQM

• Auto refresh and self refresh

• 4096 refresh cycles / 64ms

• Programmable Burst Length and Burst Type

- 1, 2, 4, 8 and Full Page for Sequence Burst

- 1, 2, 4 and 8 for Interleave Burst

• Programmable CAS Latency ; 1, 2, 3 Clocks

• Internal two banks operation

ORDERING INFORMATION

Part No.

Clock Frequency

HY57V161610ET-5I

HY57V161610ET-55I

HY57V161610ET-6I

HY57V161610ET-7I

HY57V161610ET-8I

HY57V161610ET-10I

HY57V161610ET-15I

200MHz

183MHz

166MHz

143MHz

125MHz

100MHz

66MHz

Note :

1. VDD(min) of HY57V161610ET-5I/55I is 3.15V

Organization

Interface

2Banks x 512Kbits x 16

LVTTL

Package

400mil

50pin TSOP II

This document is a general product description and is subject to change without notice. Hynix Semiconductor does not assume any responsibility for

use of circuits described. No patent licenses are implied

Rev. 0.1 / Nov. 2003

1

1 page

CAPACITANCE (TA=25°C, f=1MHz)

Parameter

Input capacitance

Data input / output capacitance

Pin

CLK

A0 ~ A10, BA

CKE, CS, RAS, CAS, WE, UDQM, LDQM

DQ0 ~ DQ15

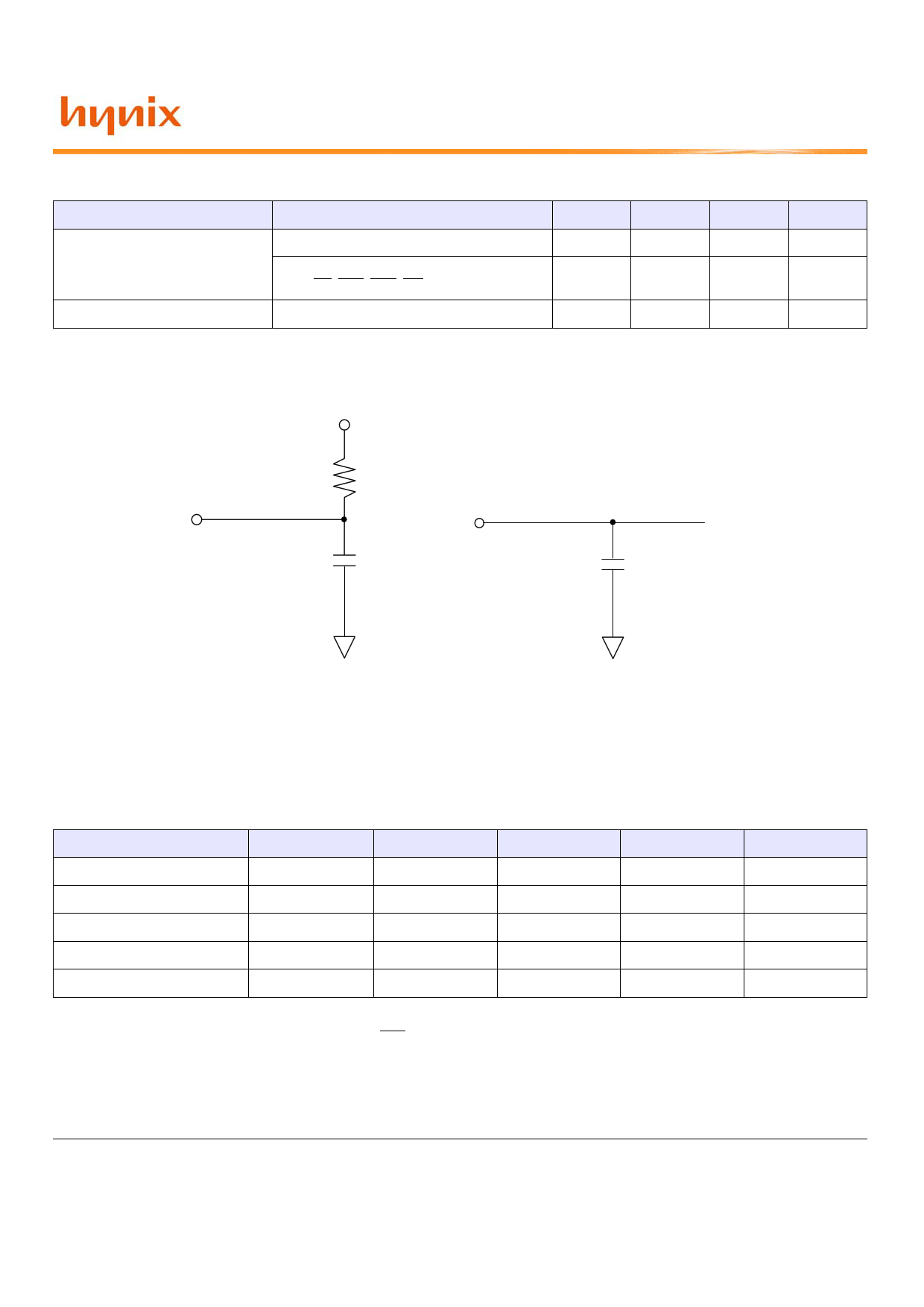

OUTPUT LOAD CIRCUIT

Output

Vtt=1.4V

RT=250 Ω

30pF

Output

HY57V161610ET-I

Symbol

CI1

CI2

CI/O

Min

2.5

2.5

4

Max

4

5

6.5

Unit

pF

pF

pF

30pF

DC Output Load Circuit

AC Output Load Circuit

DC CHARACTERISTICS I (TA=-40°C to 85°C)

Parameter

Power Supply Voltage

Input leakage current

Output leakage current

Output high voltage

Output low voltage

Symbol

VDD

IL

IO

VOH

VOL

Min.

3.0

-1

-1

2.4

-

Max

3.6

1

1

-

0.4

Note :

1.VDD(min) is 3.15V when HY57V161610ET-7I operates at CAS latency=2 and tCK2=8.9ns.

2.VDD(min) of HY57V161610ET-5I/55I is 3.15V

3.VIN = 0 to 3.6V, All other pins are not under test = 0V

4.DOUT is disabled, VOUT=0 to 3.6V

Rev. 0.1 / Nov. 2003

Unit Note

V 1, 2

uA 3

uA 4

V IOH = -4mA

V IOL =+4mA

5

5 Page

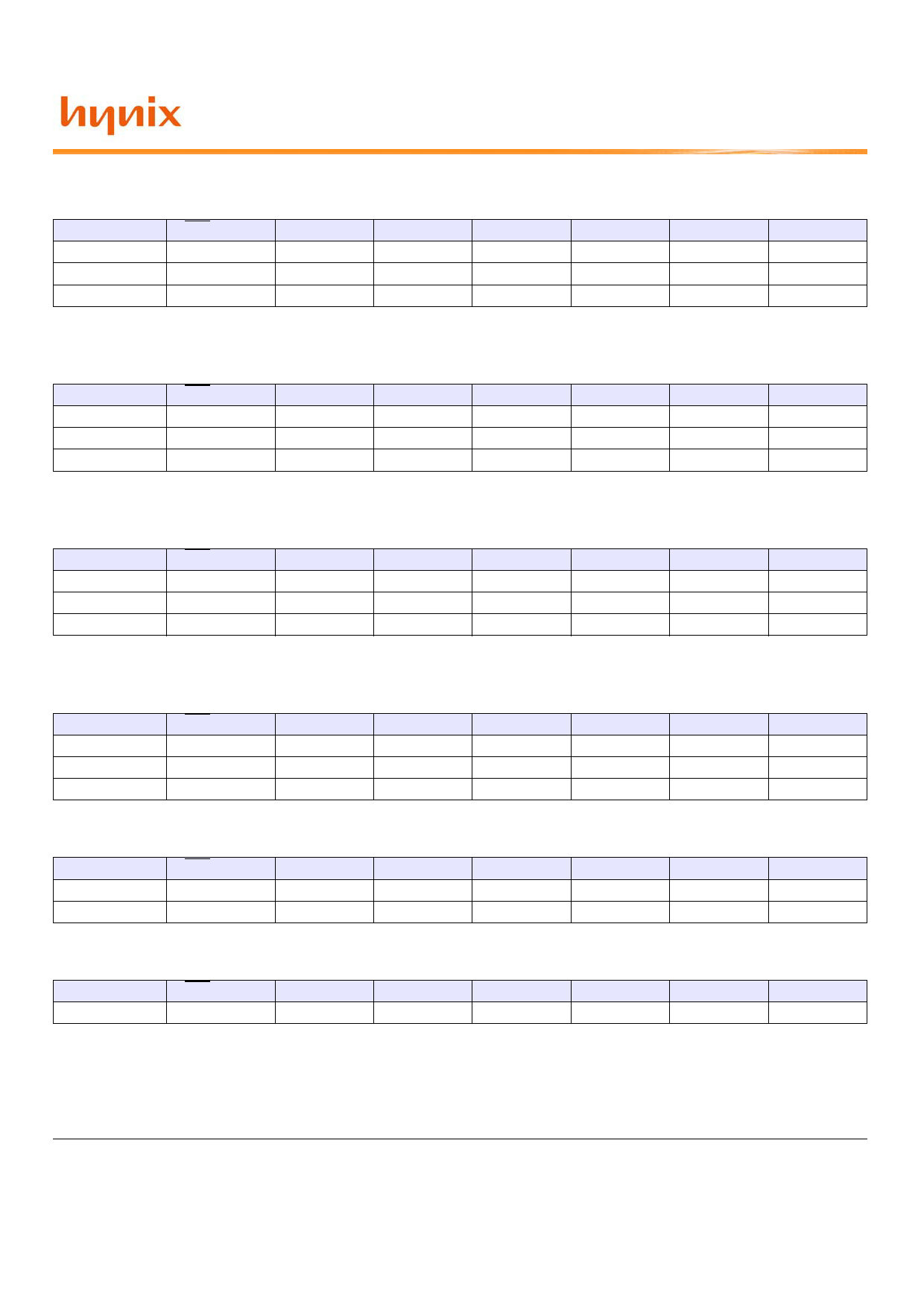

HY57V161610ET-I

HY57V161610ET-55I

183MHz

166MHz

143MHz

CAS Latency

3CLKs

3CLKs

3CLKs

tRCD

3CLKs

3CLKs

3CLKs

HY57V161610ET-6I

166MHz

143MHz

125MHz

CAS Latency

3CLKs

3CLKs

3CLKs

tRCD

3CLKs

3CLKs

2CLKs

HY57V161610ET-7I

143MHz

125MHz

100MHz

CAS Latency

3CLKs

3CLKs

2CLKs

tRCD

3CLKs

3CLKs

2CLKs

HY57V161610ET-8I

125MHz

100MHz

83MHz

CAS Latency

3CLKs

3CLKs

2CLKs

HY57V161610ET-10I

100MHz

83MHz

CAS Latency

3CLKs

2CLKs

HY57V161610ET-15I

66MHz

CAS Latency

1CLKs

tRCD

3CLKs

2CLKs

2CLKs

tRCD

2CLKs

2CLKs

tRCD

2CLKs

tRAS

7CLKs

7CLKs

7CLKs

tRC

10CLKs

10CLKs

10CLKs

tRP

3CLKs

3CLKs

3CLKs

tRAS

7CLKs

7CLKs

6CLKs

tRC

10CLKs

10CLKs

9CLKs

tRP

3CLKs

3CLKs

3CLKs

tRAS

7CLKs

6CLKs

5CLKs

tRC

10CLKs

9CLKs

7CLKs

tRP

3CLKs

3CLKs

2CLKs

tRAS

6CLKs

5CLKs

4CLKs

tRC

9CLKs

7CLKs

6CLKs

tRP

3CLKs

2CLKs

2CLKs

tRAS

5CLKs

4CLKs

tRC

7CLKs

6CLKs

tRP

2CLKs

2CLKs

tRAS

4CLKs

tRC

6CLKs

tRP

2CLKs

tAC

5ns

5.5ns

5.5ns

tAC

5.5ns

5.5ns

6ns

tAC

5.5ns

6ns

7ns

tAC

6ns

7ns

7ns

tAC

7ns

7ns

tAC

14ns

tOH

2ns

2ns

2.5ns

tOH

2ns

2.5ns

2.5ns

tOH

2.5ns

2.5ns

2.5ns

tOH

2.5ns

2.5ns

2.5ns

tOH

2.5ns

2.5ns

tOH

2.5ns

Rev. 0.1 / Nov. 2003

11

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet HY57V161610ET-10I.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HY57V161610ET-10I | 2 Banks x 512K x 16 Bit Synchronous DRAM | Hynix Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |