|

|

PDF XR28V382 Data sheet ( Hoja de datos )

| Número de pieza | XR28V382 | |

| Descripción | 3.3V DUAL LPC UART | |

| Fabricantes | Exar | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XR28V382 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

XR28V382

3.3V DUAL LPC UART WITH 128-BYTE FIFO

DECEMBER 2013

REV. 1.0.1

GENERAL DESCRIPTION

The XR28V382 (V382) is a dual Universal

Asynchronous Receiver and Transmitter (UART) for

the Intel Low Pin Count (LPC) bus interface. This

device can replace or supplement a Super I/O device

to add additinal serial ports to the system.

The V382 UARTs support any 16-bit I/O address

supported by the system. The register set is based on

the industry standard 16550 UART, so the V382

operates with standard serial port drivers without

requiring a custom driver to be installed.

The 128 byte Transmit and Receive FIFOs reduce

CPU overhead and minimize the chance of buffer

overflow and data loss. In addition to the 16550 UART

registers, there are also Configuration register set

where enhanced features such as the 9-bit (multidrop)

mode, IrDA mode and the Watchdog Timer can be

enabled.

The V382 is available in a 32-pin QFN package.

APPLICATIONS

x Industrial and Embedded PCs

x Factory Automation and Process Controls

x Network Routers

x System Board Designs

FEATURES

x 128 Byte Transmit and Receive FIFO

x Compliant to LPC 1.1 Specifications

x -40°C to +85°C Industrial Temp Operation

x Watchdog Timer with WDTOUT# signal

x 2 independent UART channels

■ Programmable I/O mapped base addresses

■ Data rates up to 3 Mbps

■ Selectable RX FIFO interrupt trigger levels

■ Auto RS-485 Half-Duplex Control mode

■ Programmable character lengths (5, 6, 7, 8)

with even, odd, or no parity

■ IrDA mode and separate IRTXA# and IRRXA#

pins for the first UART channel

■ 9-bit (Multidrop) mode

x External 24MHz/48MHz clock

x Single 3.3V Supply Voltage ( ± 10%)

x 5V tolerant inputs

x 32-QFN package (5mm x 5mm)

FIGURE 1. XR28V382 BLOCK DIAGRAM

VCC

GND

P C IR S T #

LCLK

LFRAME#

L A D [3 :0 ]

SER IR Q

3.3V ± 10%

LPC

Bus

Interface

G lobal

C o n fig u ra tio n

R e g is te rs

Baud

R a te

G e n e ra to r

TX FIFO

(IrDA Encoder)

RX FIFO

(IrDA Decoder)

Status and

C o n tro l

R egisters

M odem IOs

UART Channel A

TXA / PS_3F8_IRQA

IR TXA# / PS_CO NF_KEY0

RXA

IR RXA#

R TSA#/PS_C O NF_2E/R S485

D TR A#/PS_3E0_IR Q A

CTSA#, DSRA#, CDA#, RIA#

W D TO U T#/

PS_W D T

C L K IN

W atch

Dog

Tim er

C lock

D iv id e r

Baud

R a te

G enerator

TX FIFO

RX FIFO

Status and

C o n tro l

R e g iste rs

M odem IOs

UART Channel B

TXB / PS_2F8_IR Q B

RXB

R T S B # /P S _ C O N F _ K E Y 1 /R S 4 8 5

D T R B # /P S _ 2 E 0 _ IR Q B

CTSB#, DSRB#, CDB#,

R IB #

Exar Corporation 48720 Kato Road, Fremont CA, 94538 • (510) 668-7000 • FAX (510) 668-7017 • www.exar.com

1 page

XR28V382

REV. 1.0.1

3.3V DUAL LPC UART WITH 128-BYTE FIFO

1.0 FUNCTIONAL DESCRIPTIONS

1.1 Power on Strapping Options

At power-on, strapping options for each pin listed in Table 1 result in the register values based upon the pin

state selected. These register values can also be modified by the software.

1.1.1 UART/Watchdog Timer Options

The V382 provides five pins for power on hardware strapping options to select the settings of the UART

channels and Watchdog Timer.

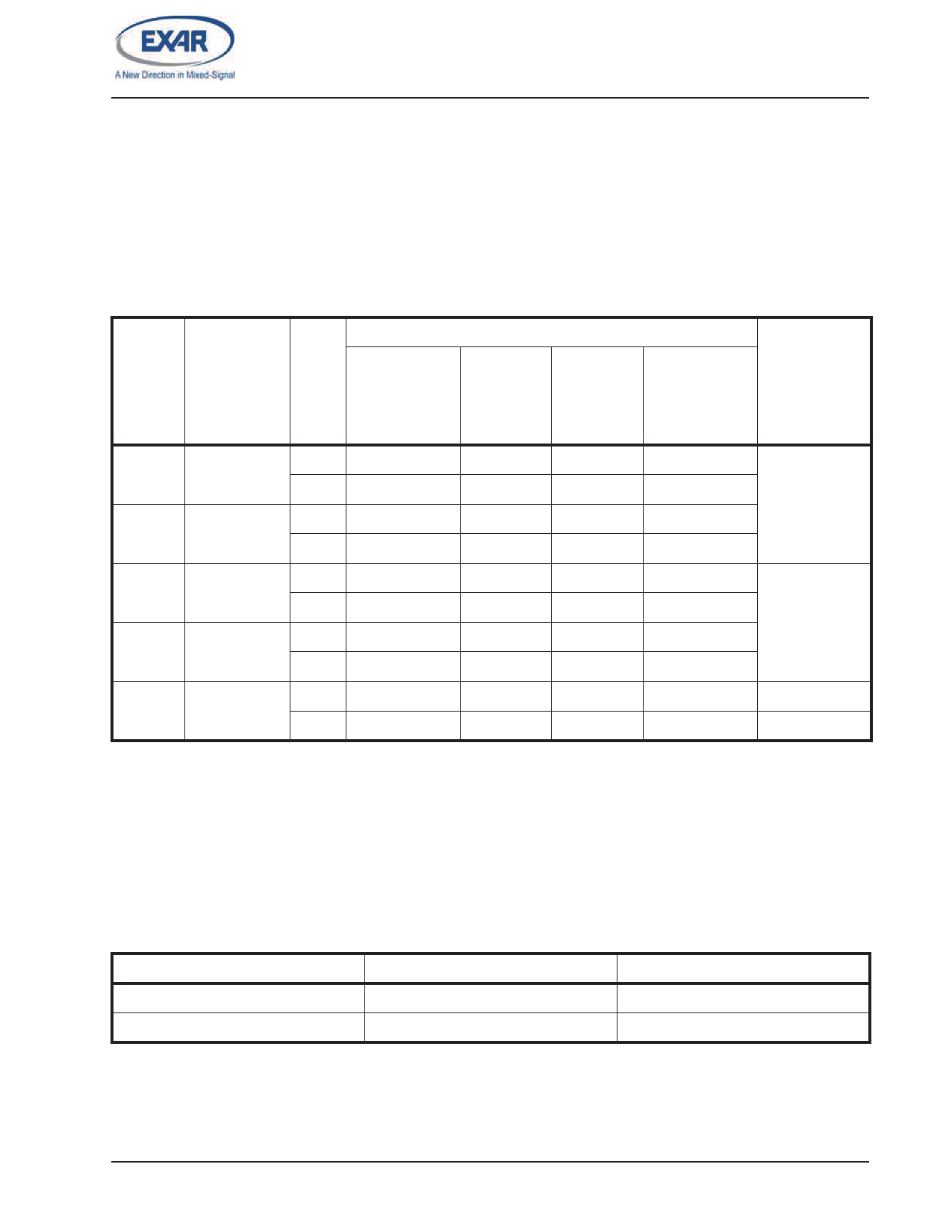

TABLE 1: UART POWER ON CONFIGURATION

REGISTER VALUES

PIN

NUMBER

PIN NAME

PIN

STATE

ENABLE

(0X30)

BASE

ADDRESS

HIGH

REGISTER

(0X60)

BASE

ADDRESS

LOW

REGISTER

(0X61)

IRQSEL

(0X70)

COMMENT

23

DTRB# /

1

PS_2E0_IRQB

0

25

TXB /

1

PS_2F8_IRQB

0

0x1

0x0

0x1

0x0

0x2 0xE0

0x0 0x0

0x2 0xF8

0x0 0x0

0x4

0x0

When both pins

are high, the

0x4 base address

will be 0x2F8.

0x0

27

DTRA# /

1

PS_3E0_IRQA

0

29

TXA /

1

PS_3F8_IRQA

0

0x1

0x0

0x1

0x0

0x3 0xE0

0x0 0x0

0x3 0xF8

0x0 0x0

0x3

0x0

When both pins

are high, the

0x3 base address

will be 0x3F8.

0x0

19

WDTOUT# /

1

PS_WDT

0

0x1

0x0

0x4 0x42

0x0 0x0

0x0

0x0

After power-on, the Enable, Base Address High & Low, IRQSEL registers can be modified by the software.

1.1.2 Configuration Port and Key Selection Options

1.1.2.1 Configuration Port Selection Option

The configuration registers are programmed by the index port and the data port. The port address is

determined by the strap pin RTSA#/PS_CONF_2E/RS485. If an external pull-down resistor is not installed, the

default value of the RTSA#/PS_CONF_2E/RS485 pin is ’1’ when the system powers on. Therefore, the default

index port address is 0x2E and the data port address is 0x2F.

TABLE 2: CONFIGURATION PORT SELECTION

RTSA#/PS_CONF_2E/RS485 (PIN 26)

INDEX PORT ADDRESS

DATA PORT ADDRESS

0

0x4E

0x4F

1 (default)

0x2E

0x2F

5

5 Page

XR28V382

REV. 1.0.1

3.3V DUAL LPC UART WITH 128-BYTE FIFO

1.4.2.3 Transmitter Operation in FIFO Mode

The host may fill the transmit FIFO with up to 128 bytes of transmit data. The THR empty flag (LSR bit-5) is set

whenever the FIFO is empty. The THR empty flag can generate a transmit empty interrupt (ISR bit-1) when the

FIFO becomes empty. The transmit empty interrupt is enabled by IER bit-1. The TSR flag (LSR bit-6) is set

when TSR/FIFO becomes empty.

FIGURE 4. TRANSMITTER OPERATION IN FIFO MODE

Transmit

Data Byte

Transmit

FIFO

THR Interrupt (ISR bit-1) when TX

FIFO becomes empty. FIFO is

enabled by FCR bit-0=1

Clock

Transmit Data Shift Register

(TSR)

TXFIFO1

1.4.3 Receiver

The receiver section contains an 8-bit Receive Shift Register (RSR) and up to 128 bytes of FIFO which

includes a byte-wide Receive Holding Register (RHR). The RSR uses the internal sampling clock for timing. It

verifies and validates every bit on the incoming character in the middle of each data bit. On the falling edge of a

start or false start bit, an internal receiver counter starts counting at the clock rate. After 8 clocks the start bit

period should be at the center of the start bit. At this time the start bit is sampled and if it is still a logic 0 it is

validated. Evaluating the start bit in this manner prevents the receiver from assembling a false character. The

rest of the data bits and stop bits are sampled and validated in this same manner to prevent false framing. If

there were any error(s), they are reported in the LSR register bits 2-4. Upon unloading the receive data byte

from RHR, the receive FIFO pointer is bumped and the error tags are immediately updated to reflect the status

of the data byte in RHR register. RHR can generate a receive data ready interrupt upon receiving a character

or delay until it reaches the FIFO trigger level. Furthermore, data delivery to the host is guaranteed by a receive

data ready time-out interrupt when data is not received for 4 word lengths as defined by LCR[1:0] plus 12 bits

time. This is equivalent to 3.7-4.6 character times. The RHR interrupt is enabled by IER bit-0. See Figure 5.

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet XR28V382.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XR28V382 | 3.3V DUAL LPC UART | Exar |

| XR28V384 | 3.3V QUAD LPC UART | Exar |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |