|

|

PDF NCS36510 Data sheet ( Hoja de datos )

| Número de pieza | NCS36510 | |

| Descripción | Low Power System-on-Chip | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de NCS36510 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

NCS36510

Low Power System-on-Chip

For 2.4 GHz IEEE

802.15.4-2006 Applications

The NCS36510 is a low power, fully integrated, System on Chip

that integrates a 2.4 GHz IEEE 802.15.4−2006 compliant transceiver,

ARM® Cortex®−M3 microprocessor, RAM and FLASH memory, a

true random number generator, and multiple peripherals to support

design of a complete and secure wireless network with minimal

external components.

The NCS36510 offers advanced power management techniques that

allow operation down to supply voltages as low as 1 V while

minimizing current consumption. The NCS36510 is specifically

designed for applications requiring maximum battery life while

minimizing cost.

The NCS36510 incorporates an industry leading 32 bit

ARM Cortex−M3 for high performance, low power and low cost

processing. The NCS36510 includes 640 kB of embedded FLASH

memory for program storage along with 48 kB of RAM for data storage.

NCS36510 uses a hardware accelerated MAC to minimize

processor overhead while maximizing available processor power for

running application software.

Peripherals include DMA, UART(2), SPI(2), I2C(2), PWM, RTC,

three programmable timers, WDT, 18 GPIO, 10 bit ADC with four

external inputs and integrated temperature and voltage sensors.

Features

• Low Voltage Operation to as low as 1.0 V

• 0.18 mA Coma Mode Leakage Current

• 0.65 mA Coma Mode Sleep Current

• 6.6 mW Receive Power Consumption

• −99 dBm Receiver Sensitivity

• 6.9 mW Transmit Power Consumption

• Programmable Output Power to X8 dBm

• 2.4 GHz IEEE 802.15.4−2006 Transceiver

• ARM Cortex − M3 Processor

• AES 128/256 Encryption Engine

• True Random Number Generator

• 640 kB Embedded FLASH Memory

• 48 kB Internal RAM Memory

Typical Applications

• Internet of Things

• Building and Industrial Automation

• ZigBee® / 6LoWPAN / WirelessHART® / Threadt

www.onsemi.com

MARKING

DIAGRAM

1 40

40 PIN QFN, 6x6

MN SUFFIX

CASE 488AR

NCS36510

AWLYYWWG

A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

G = Pb−Free Package

ORDERING INFORMATION

See detailed ordering and shipping information on page 33 of

this data sheet.

© Semiconductor Components Industries, LLC, 2016

September, 2016 − Rev. 0

1

Publication Order Number:

NCS36510/D

1 page

NCS36510

PIN ASSIGNMENT

Table 1. 40−PIN QFN CONFIGURATION

Pin Pin Name

Description

1

DIO[10]

General Purpose Digital I/O

2

DIO[9]

General Purpose Digital I/O

3

DIO[8]

General Purpose Digital I/O

4

DIO[16]

General Purpose Digital I/O

5

VDDIO

Digital I/O Bank Power

6

DIO[15]

General Purpose Digital I/O

7

DIO[7]

General Purpose Digital I/O

8

DIO[6]

General Purpose Digital I/O

9

DIO[5]

General Purpose Digital I/O

10

DIO[4]

General Purpose Digital I/O

11

DIO[3]

General Purpose Digital I/O

12

DIO[2]

General Purpose Digital I/O

13

DIO[1]

General Purpose Digital I/O

14

DIO[0]

General Purpose Digital I/O

15

DIO[14]

General Purpose Digital I/O

16

DVDD

Digital 950 mV Regulator

17

FVDDHI

Embedded FLASH 1.8 V Regulator, Input to external filter required for 1 V mode

18

FVDDHO

Embedded FLASH 1.8 V Regulator, Output from external filter required for 1 V mode

19 NC Tie to GND or leave floating

20

V1VO

Core 1.1 V Regulator, Output to external filter required for 3 V mode using the switching regulator

21

V1VI

Core 1.1 V Regulator, Input to external filter required for 3 V mode using the switching regulator

22 V3V Main power input

23 A0 ADC Channel Input

24 A1 ADC Channel Input

25

X32MO

32 MHz Crystal Output

26

X32MI

32 MHz Crystal Input

27

X32K0

32.768 kHz Crystal Output

28

X32KI

32.768 kHz Crystal Input

29 A2 ADC Channel Input

30 A3 ADC Channel Input

31 RX RF LNA Input

32 TX RF PA Output

33

RFPWR

RF PA Regulator Output

34 VPA RF PA Regulator Input

35

TEST

Test Input (used to enable SWD Interface)

36

RESETN

Active Low Reset

37

DIO[13]

General Purpose Digital I/O

38

DIO[12]

General Purpose Digital I/O

39

DIO[11]

General Purpose Digital I/O

40

DIO[17]

General Purpose Digital I/O

EP Exposed Pad GND, thermal pad under package

www.onsemi.com

5

5 Page

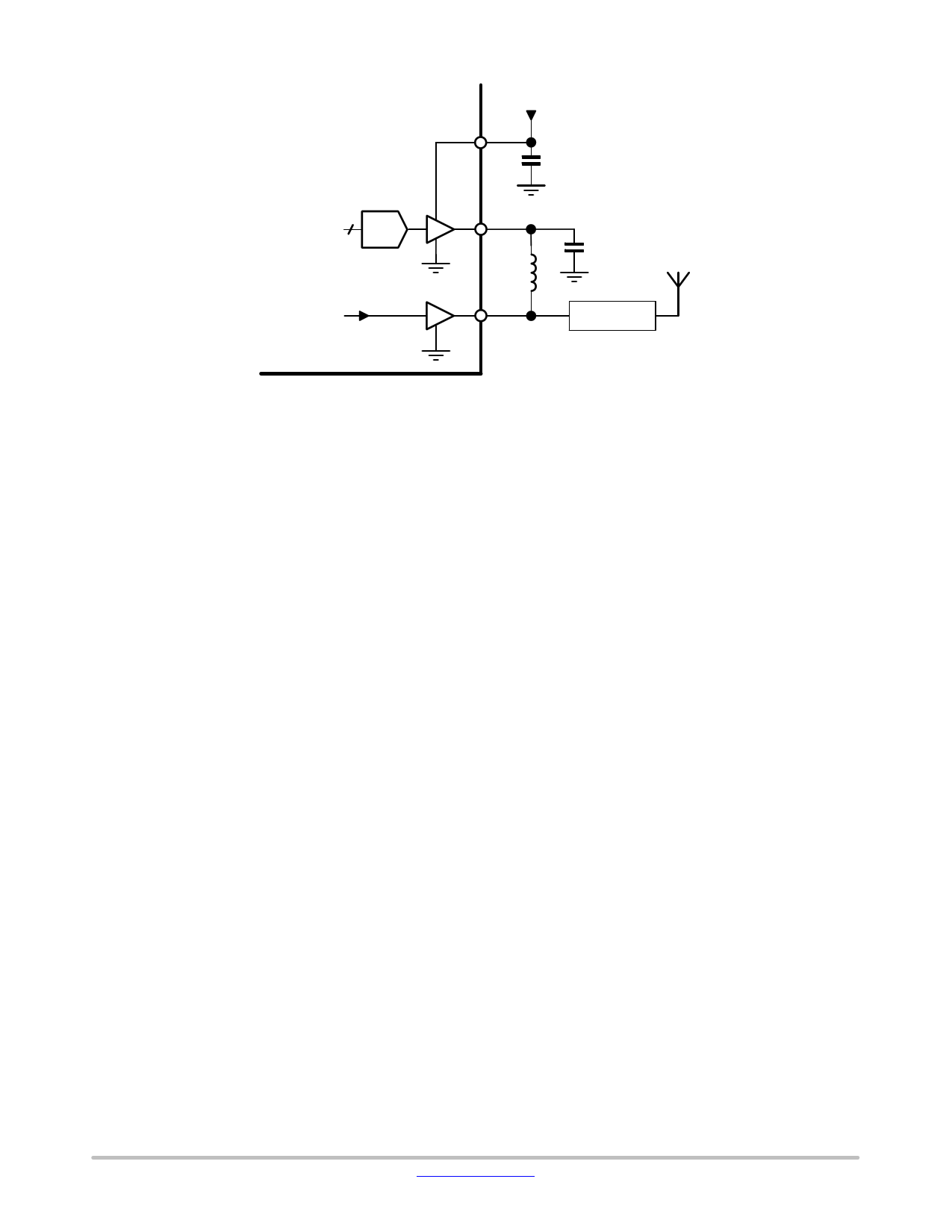

NCS36510

34 VPA

PWRADJ

DAC

33 RFPWR

TX_IN

32 TX

RF Match

NCS36510

DC20140606.2

Figure 6. Transmitter

The PA requires an external inductor from the Tx pin to the

RFPWR pin.

The supply voltage at VPA can be from 1 V to 3.6 V,

independently from the other power domains. Typically

VPA is connected to V3V.

The RF output power is determined by the power setting

set at the RFPWR regulator. The maximum DC voltage at

RFPWR is about 2 V. When the transmitter is off, the

RFPWR node is pulled to ground through an internal switch.

Antenna Diversity

Using a single antenna in a RF multi−path environment

may make it difficult to receive signals consistently. To

combat this natural phenomenon, antenna diversity control

support is offered. Antenna diversity requires an external

antenna switch to switch between two separate antennas

located at least a quarter wavelength away from each other.

Using a GPIO port, an external antenna switch can be

automatically switched to maximize sensitivity.

MODEM

The NCS36510 modem combines a proprietary blend of

hardware and software to implement the requirements of the

IEEE 802.15.4−2006 standard. By efficiently splitting the

hardware and software interface for the modem, processor

bandwidth is maximized and power consumption is

minimized.

PERIPHERAL DEVICES

PERIPHERAL API

The software development kit contains drivers for all the

NCS36510 peripherals. Each peripheral can be initialized

and operated through an API.

PERIPHERAL ENABLE AND DISABLE

To save power, the clock to each peripheral can be gated

off. Writes to the disabled peripherals are ignored.

CROSS BAR

NCS36510 has 18 digital IO pins to communicate with

external devices. These pins are shared between the

following internal peripheral devices:

1. UART 1

2. UART 2

3. I2C 1

4. I2C 2

5. SPI 1

6. SPI 2

7. PWM

8. GPIO

9. SWD

The application needs to configure the cross bar to wire

the desired peripheral device to the desired IO pins, given

the system constraints. The tables below indicate what

peripheral device can be wired to what pin.

www.onsemi.com

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet NCS36510.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NCS36510 | Low Power System-on-Chip | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |