|

|

PDF CLC014 Data sheet ( Hoja de datos )

| Número de pieza | CLC014 | |

| Descripción | Adaptive Cable Equalizer for High-Speed Data Recovery | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CLC014 (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

June 1998

CLC014

Adaptive Cable Equalizer for High-Speed Data Recovery

General Description

National’s CLC014 adaptive cable equalizer is a low-cost

monolithic solution for equalizing data transmitted over cable

(or any media with similar dispersive loss characteristics).

The CLC014 simplifies the task of high-speed data recovery

with a one-chip solution and a minimal number of external

components. The equalizer automatically adapts to equalize

any cable length from zero meters to lengths that attenuate

the signal by 40 dB at 200 MHz. This corresponds to 300

meters of Belden 8281 or 120 meters of Category 5 UTP

(unshielded twisted pair).

The CLC014 provides superior jitter performance:

180pspp for 270 Mbps data that has passed through 200

meters of Belden 8281 cable. This exceptional perfor-

mance provides wide error margin in digital data links.

The equalizer operates on a single supply with a power con-

sumption of only 290 mW. The small 14-pin SOIC package

allows for high-density placement of components for multi-

channel applications such as routers. The equalizer oper-

ates over a wide range of data rates from less than 50 Mbps

to rates in excess of 650 Mbps.

The equalizer is flexible in allowing either single-ended or

differential input drive. Its high common mode rejection pro-

vides excellent immunity to interference from noise sources.

On-chip quantized feedback eliminates baseline wander.

Additional features include a carrier detect output and an

output mute pin which, when tied together, mute the output

when no signal is present. A buffered eye monitor output is

provided, for viewing the equalized signal prior to the com-

parator. Differential AEC pins allow the user to set the inter-

nal adaptive loop time constant with one external capacitor.

Also, the CLC014 is insensitive to the pathological patterns

inherent in the video industry standards.

Features

n Automatic equalization of coaxial and twisted pair cables

n Carrier detection and output mute

n Output eye monitor

n Single supply operation: +5V or −5.2V

n Single-ended or differential input

n Low cost

Applications

n SMPTE 259M serial digital interfaces: NTSC/PAL, 4:2:2

component and wide screen; also 540 Mbps (4:4:4:4)

n Serial digital video routing and distribution

n Serial digital data equalization and reception

n Data recovery equalization: ATM, CAD networks,

medical, set top terminals, industrial video networks

Key Specifications

n Low jitter: 180pspp @ 270 Mbps through 200 meters of

Belden 8281 coaxial cable

n High data rates: < 50 Mbps to > 650 Mbps

n Excellent input return loss: 19 dB @ 270 MHz

n Low supply current: 58 mA

n Equalizes up to 300+ meters of Belden 8281 or 120

meters of Cat 5 UTP cable

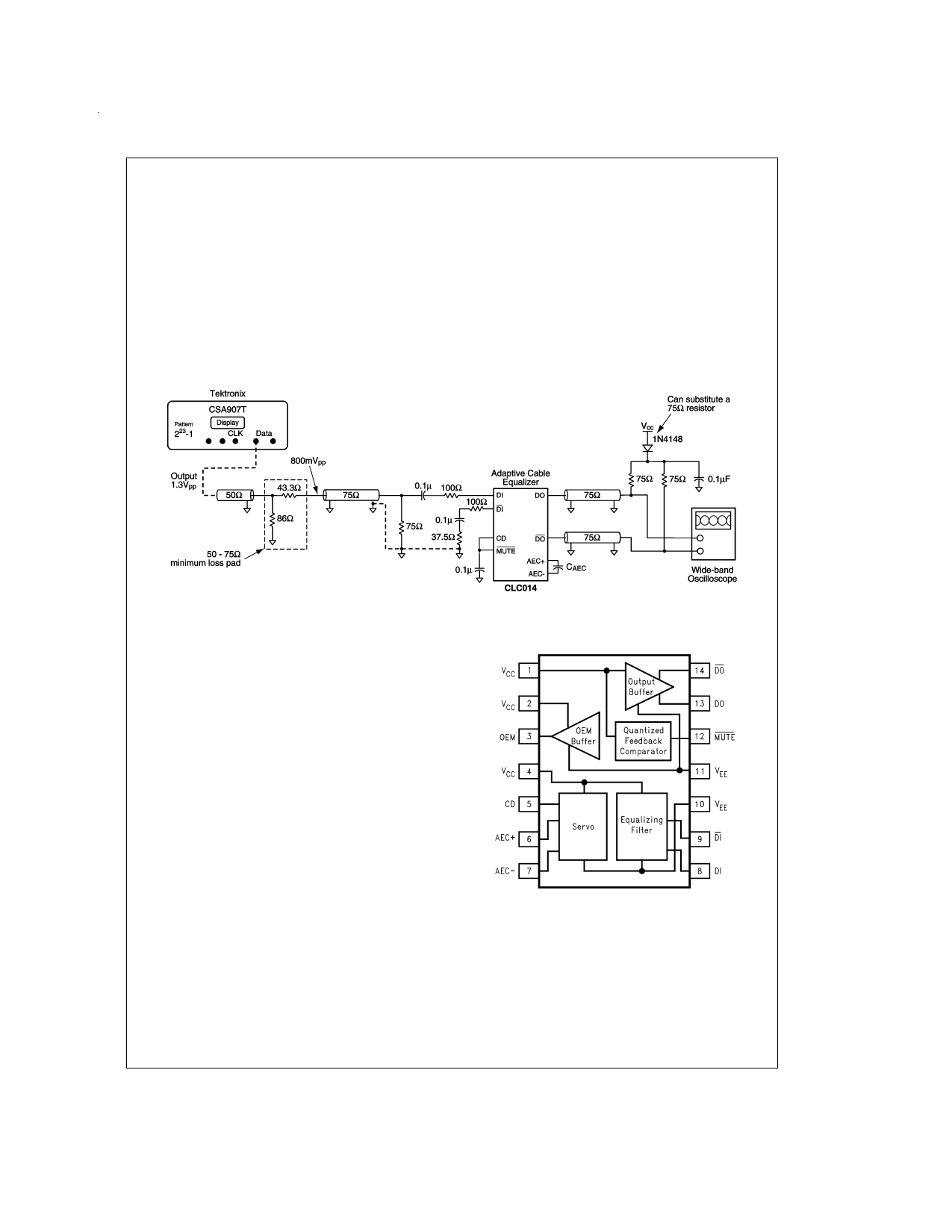

Typical Application

© 1999 National Semiconductor Corporation DS100056

DS100056-4

www.national.com

1 page

Typical Performance Characteristics

Before Equalization:

100m of Belden 8281 Coaxial Cable

After Equalization:

100m of Belden 8281 Coaxial Cable

Data Rate: 270Mbps

Time (1ns/div)

DS100056-5

Before Equalization:

200m of Belden 8281 Coaxial Cable

Data Rate: 270Mbps

Time (1ns/div)

DS100056-8

After Equalization:

200m of Belden 8281 Coaxial Cable

Data Rate: 270Mbps

Time (1ns/div)

DS100056-6

Before Equalization:

300m of Belden 8281 Coaxial Cable

Data Rate: 270Mbps

Time (1ns/div)

DS100056-9

After Equalization:

300m of Belden 8281 Coaxial Cable

Data Rate: 270Mbps

Time (1ns/div)

DS100056-7

Data Rate: 270Mbps

Time (1ns/div)

DS100056-10

5 www.national.com

5 Page

Layout and Measurement

The printed circuit board layout for the CLC014 requires

proper high-speed layout to achieve the performance speci-

fications found in the datasheet. The following list contains a

few rules to follow:

1. Use a ground plane.

2. Decouple power pins with 0.1 µF capacitors placed

≤ 0.1” (3mm) from the power pins.

3. Design transmission strip lines from the CLC014’s input

and output pins to the board connectors.

4. Route outputs away from inputs.

5. Keep ground plane ≥ 0.025” (0.06mm) away from the in-

put and output pads.

Figure 8 shows a block level measurement diagram, while

Figure 15 on depicts a detailed schematic. A pseudo-random

pattern generator with low output jitter was used to provide a

NRZI pattern to create the eye diagrams shown in the Typi-

cal Performance Characteristics section.

Since most pattern generators have a 50Ω output imped-

ance, a translation can be accomplished using a CLC006

Cable Driver as an impedance transformer. A wide band-

width oscilloscope is needed to observe the high data rate

eye pattern. When monitoring a single output that is termi-

nated at both the equalizer output and the oscilloscope, the

effective output load is 37.5Ω. Consequently, the signal

swing is half that observed for a single-ended 75Ω

termination.

FIGURE 8. Typical Measurement Block

Troubleshooting with scope probes can affect the equaliza-

tion. For high data rates, use a low capacitance probe with

less than 2 pF probe capacitance. Evaluation boards and lit-

erature are available for quick prototyping and evaluation of

the CLC014 Adaptive Cable Equalizer. The CLC014 con-

tains CMOS devices and operators should use grounding

straps when handling the parts.

Figure 9 shows the CLC014’s internal power supply routing.

Bypass VCC (pin 4) by:

• Monolithic capacitor of about 0.1 µF placed less than 0.1”

(3mm) from the pin

• Tantalum capacitor of about 6.8 µF for large current sig-

nal swings placed as close as convenient to the CLC014

DS100056-28

DS100056-29

FIGURE 9. Power Package Routing Fixture

To minimize ringing at the CLC014’s inputs, place a 100Ω re-

sistor in series with the input. This resistor reduces induc-

tance effects.

Several layout techniques can improve high speed perfor-

mance:

• Keep input, output and AEC traces well separated

• Use balanced input termination’s

• Avoid routing traces close to the CLC014’s input trace

11 www.national.com

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet CLC014.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CLC011 | Serial Digital Video Decoder | National Semiconductor |

| CLC011 | CLC011 Serial Dig Video Decoder (Rev. D) | Texas Instruments |

| CLC011ACQ | Serial Digital Video Decoder | National Semiconductor |

| CLC011BCQ | Serial Digital Video Decoder | National Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |