|

|

PDF NT5TU64M16HZ Data sheet ( Hoja de datos )

| Número de pieza | NT5TU64M16HZ | |

| Descripción | Industrial and Automotive DDR2 1Gb SDRAM | |

| Fabricantes | Nanya | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de NT5TU64M16HZ (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

D1GDbR2D1DGRb2 SDRAM H-Die

NT5TU128M8HE / NT5TU64M16HG(Z)

Nanya Technology Corp.

NT5TU128M8HE / NT5TU64M16HG(Z)

Commercial, Industrial and Automotive DDR2 1Gb SDRAM

Features

JEDEC DDR2 Compliant

- Double-data rate on DQs, DQS, DM bus

- 4n Prefetch Architecture

Throughput of valid Commands

- Posted CAS and Additive Latency (AL)

Signal Integrity

- Configurable DS for system compatibility

- Configurable On-Die Termination

Data Integrity

- Auto Refresh and Self Refresh Modes

Power Saving Modes

- Power Down Mode

- Partial Array Self Refresh (PASR)

SSTL_18 compliance and Power Supply

- VDD/VDDQ = 1.70 to 1.90V

Options

Speed Grade ( DataRate/CL-tRCD-tRP)

- 1066 Mbps / 7-7-7

- 800 Mbps / 5-5-5

Additional Features

- OCD adjustment Mode for DS tuning 1

Temperature Range (Tc) 2

- Commercial Grade = 0℃ to + 95℃

- Industrial Grade (-I)= - 40℃ to + 95℃

- Automotive Grade 2 (-H)= - 40℃ to + 105℃

- Automotive Grade 3(-A) = - 40℃ to + 95℃

Programmable functions

Output Drive Impedance (Full, Reduced)

Burst Length (4, 8)

Burst Type (Sequential, Interleaved)

Rtt (50, 75, 150)

CAS Latency (5, 6, 7)

Additive Latency (0, 1, 2, 3, 4, 5, 6)

WR (2, 3, 4, 5, 6, 7, 8)

PASR (full, 3/4, 1/2, 1/4, 1/8)

Package / Density information

Lead-free RoHS compliance and Halogen-free

Density and Addressing

1Gb

(Org / Package)

Length x Width Ball pitch

(mm)

(mm)

128Mb x 8

64Mb x 16

60-ball

TFBGA

84-ball

TFBGA

84-ball

VFBGA

8.00 x 10.00(E)

8.00 x 12.50(G)

8.00 x 12.50(Z)

0.80

0.80

0.80

Configuration

Number of Banks

Bank Address

Auto Precharge

Row Address

Column Address

Page Size

128Mb x 8

8

BA0 - BA2

A10/AP

A0 - A13

A0 - A9

1 KB

64Mb x 16

8

BA0 - BA2

A10/AP

A0 - A12

A0 - A9

2 KB

Notes:

1. This is enabled by using an electrical fuse. Please contact with NTC for the demand.

2. If TC exceeds 85°C, the DRAM must be refreshed externally at 2x refresh. It is required to set tREFI=3.9μs in auto refresh mode and to

set ‘1’ for EMRS (2) bit A7 in self refresh mode.

Version 1.9

03/2016

1

NTC has the rights to change any specifications or product without notification.

Nanya Technology Corporation ©

All Rights Reserved

1 page

1Gb DDR2 SDRAM

NT5TU128M8HE / NT5TU64M16HG(Z)

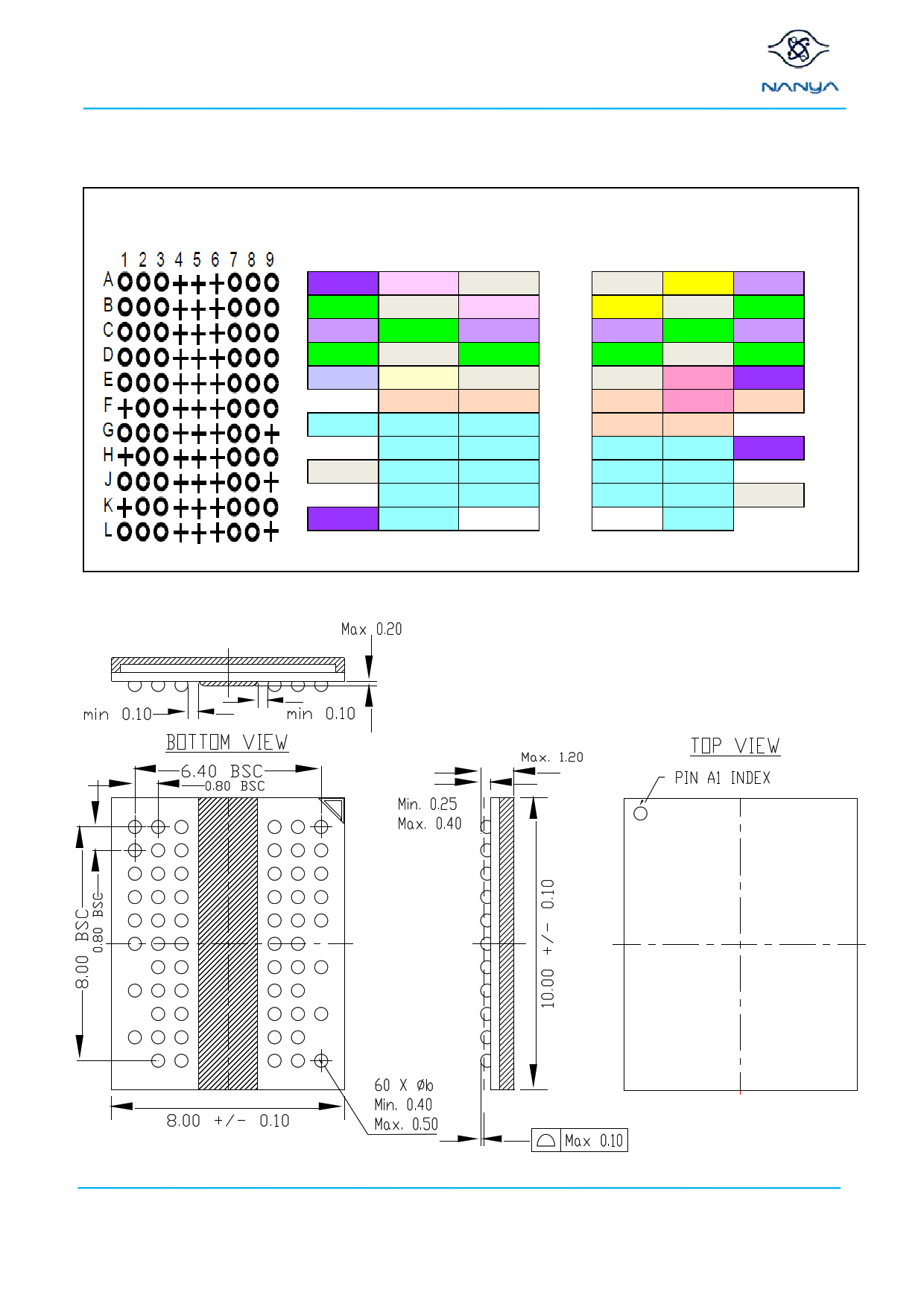

60-ball TFBGA Ballout and Package Outline Drawing (X8)

< TOP View>

See the balls through the package

1

A VDD

B DQ6

C VDDQ

D DQ4

E VDDL

F

G BA2

H

J VSS

K

L VDD

1

2

NU/RDQS

VSSQ

DQ1

VSSQ

VREF

CKE

BA0

A10/AP

A3

A7

A12

2

3

VSS

DM/RDQS

VDDQ

DQ3

VSS

WE

BA1

A1

A5

A9

NC

3

456

456

7

VSSQ

DQS

VDDQ

DQ2

VSSDL

RAS

CAS

A2

A6

A11

NC

7

8

DQS

VSSQ

DQ0

VSSQ

CK

CK

CS

A0

A4

A8

A13

8

9

VDDQ

DQ7

VDDQ

DQ5

VDD

ODT

VDD

VSS

9

A

B

C

D

E

F

G

H

J

K

L

Unit: mm

* BSC (Basic Spacing between Center)

Version 1.9

03/2016

5

Nanya Technology Corporation ©

All Rights Reserved

5 Page

1Gb DDR2 SDRAM

NT5TU128M8HE / NT5TU64M16HG(Z)

Power-up and Initialization

DDR2 SDRAMs must be powered up and initialized in a predefined manner. Operational procedures other than those

specified may result in undefined operation.

The following sequence is required for POWER UP and Initialization.

1. Either one of the following sequence is required for Power-up.

(1)

While applying power, attempt to maintain CKE below 0.2 x VDDQ and ODT at a Low state (all other inputs may be

undefined) The VDD voltage ramp time must be no greater than 200ms from when VDD ramps from 300mV to VDD

min; and during the VDD voltage ramp up, IVDD-VDDQI≦0.3 volts. Once the ramping of the supply voltages is

complete (when VDDQ crosses VDDQ min), the supply voltage specifications in Re-commanded DC operating

conditions table.

- VDD, VDDL, and VDDQ are driven from a signal power converter output, AND

- VTT is limited to 0.95V max, AND

- Vref tracks VDDQ/2; Vref must be within ±300mV with respect to VDDQ/2 during supply ramp time.

- VDDQ>=VREF must be met at all times.

(2)

While applying power, attempt to maintain CKE below 0.2 x VDDQ and ODT at a Low state, all other inputs may be

undefined, voltage levels at I/Os and outputs must be less than VDDQ during voltage ramp time to avoid DRAM

latch-up. During the ramping of the supply voltages, VDD≧VDDL≧VDDQ must be maintained and is applicable to

both AC and DC levels until the ramping of the supply voltages is complete, which is when VDDQ crosses VDDQ min.

Once the ramping of the supply voltages is complete, the supply voltage specifications provided in Re-commanded DC

operating conditions table.

- Apply VDD/VDDL before or at the same time as VDDQ.

- VDD/VDDL voltage ramp time must be no greater than 200ms from when VDD ramps from 300mV to VDDmin.

- Apply VDDQ before or at the same time as VTT.

- The VDDQ voltage ramp time from when VDD min is achieved on VDD to when VDDQ min is achieved on VDDQ

must be no greater than 500ms. (Note: While VDD is ramping, current may be supplied from VDD through the

DRAM to VDDQ.)

- Vref must track VDDQ/2; Vref must be within ±300mV with respect to VDDQ/2 during supply ramp time.

- VDDQ ≧ VREF must be met at all time.

- Apply VTT.

2. Start clock (CK, CK) and maintain stable condition.

Version 1.9

03/2016

11

Nanya Technology Corporation ©

All Rights Reserved

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet NT5TU64M16HZ.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NT5TU64M16HG | Industrial and Automotive DDR2 1Gb SDRAM | Nanya |

| NT5TU64M16HZ | Industrial and Automotive DDR2 1Gb SDRAM | Nanya |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |