|

|

PDF WM8782A Data sheet ( Hoja de datos )

| Número de pieza | WM8782A | |

| Descripción | Stereo ADC | |

| Fabricantes | Wolfson Microelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de WM8782A (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

w

24-Bit, 192kHz Stereo ADC

WM8782A

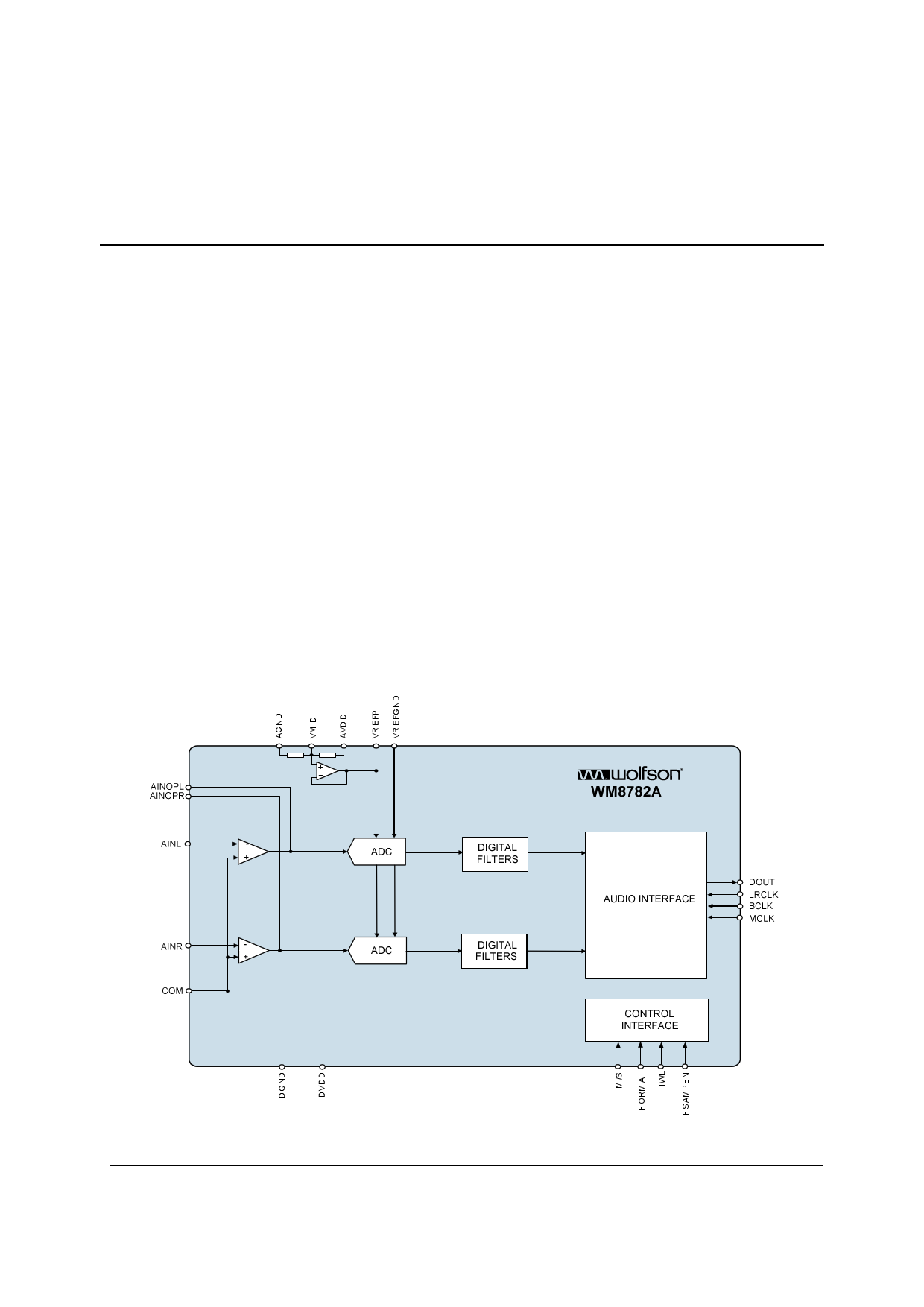

DESCRIPTION

The WM8782A is a high performance, low cost stereo

audio ADC designed for recordable media applications.

The device offers stereo line level inputs along with two

control input pins (FORMAT, IWL) to allow operation of the

audio interface in three industry standard modes. An

internal op-amp is integrated on the front end of the chip to

accommodate analogue input signals greater than 1Vrms.

The device also has a high pass filter to remove residual

DC offsets.

WM8782A offers a Slave mode clocking scheme. A stereo

24-bit multi-bit sigma-delta ADC is used with 128x, 64x or

32x over-sampling, according to sample rate. Digital audio

output word lengths from 16-24 bits and sampling rates

from 8kHz to 192kHz are supported.

The device is a hardware controlled device and is supplied

in a 20-lead SSOP.

The device is available over a functional temperature range of

-40°C to +85°C

BLOCK DIAGRAM

FEATURES

• SNR 100dB (‘A’ weighted @ 48kHz)

• THD -93dB (at –1dB)

• Sampling Frequency: 8 – 192kHz

• Slave Clocking Mode

• System Clock (MCLK): 128fs, 192fs, 256fs, 384fs, 512fs,

768fs

• Audio Data Interface Modes

- 16-24 bit I2S, 16-24 bit Left, 16-24 bit Right Justified

• Supply Voltages

- Analogue: 2.7 to 5.5V

- Digital core: 2.7V to 3.6V

• 20-lead SSOP package

• Accelerated Lifetime Screened Devices available.

APPLICATIONS

• Recordable DVD Players

• Personal Video Recorders

• STB

• Studio Audio Processing Equipment

• Automotive

WOLFSON MICROELECTRONICS plc

To receive regular email updates, sign up at http://www.wolfsonmicro.com/enews

Production Data, April 2010, Rev 4.8

Copyright ©2010 Wolfson Microelectronics plc

1 page

Production Data

WM8782A

ABSOLUTE MAXIMUM RATINGS

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously

operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given

under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible

to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage

of this device.

Wolfson tests its package types according to IPC/JEDEC J-STD-020B for Moisture Sensitivity to determine acceptable storage

conditions prior to surface mount assembly. These levels are:

MSL1 = unlimited floor life at <30°C / 85% Relative Humidity. Not normally stored in moisture barrier bag.

MSL2 = out of bag storage for 1 year at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

MSL3 = out of bag storage for 168 hours at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

The Moisture Sensitivity Level is specified in Ordering Information.

CONDITION

Digital supply voltage

Analogue supply voltage

Voltage range digital inputs

Voltage range analogue inputs

Ambient temperature (supplies applied)

Storage temperature

Pb free package body temperature (reflow 10 seconds)

Package body temperature (soldering 2 minutes)

Notes:

1. Analogue and digital grounds must always be within 0.3V of each other.

MIN

-0.3V

-0.3V

DGND -0.3V

AGND -0.3V

-55°C

-65°C

MAX

+4.5V

+7V

DVDD + 0.3V

AVDD +0.3V

+125°C

+150°C

+260°C

+183°C

THERMAL PERFORMANCE

PARAMETER

Thermal resistance – junction to

ambient

SYMBOL

RθJA

TEST CONDITIONS

MIN TYP

81

See note 1

MAX

Notes:

1. Figure given for package mounted on 4-layer FR4 according to JESD51-7. (No forced air flow is assumed).

2. Thermal performance figures are estimated.

UNIT

°C/W

w

PD, April 2010, Rev 4.8

5

5 Page

Production Data

DIGITAL AUDIO INTERFACE

The digital audio interface uses three pins:

• DOUT: ADC data output

• LRCLK: ADC data alignment clock

• BCLK: Bit clock, for synchronisation

WM8782A

The digital audio interface takes the data from the internal ADC digital filters and places it on DOUT

and LRCLK. DOUT is the formatted digital audio data stream output from the ADC digital filters with

left and right channels multiplexed together. LRCLK is an alignment clock that controls whether Left

or Right channel data is present on the DOUT line. DOUT and LRCLK are synchronous with the

BCLK signal with each data bit transition signified by a BCLK high to low transition. DOUT is always

an output. BCLK and LRCLK are always inputs.

Three different audio data formats are supported:

• Left justified

• Right justified

• I2S

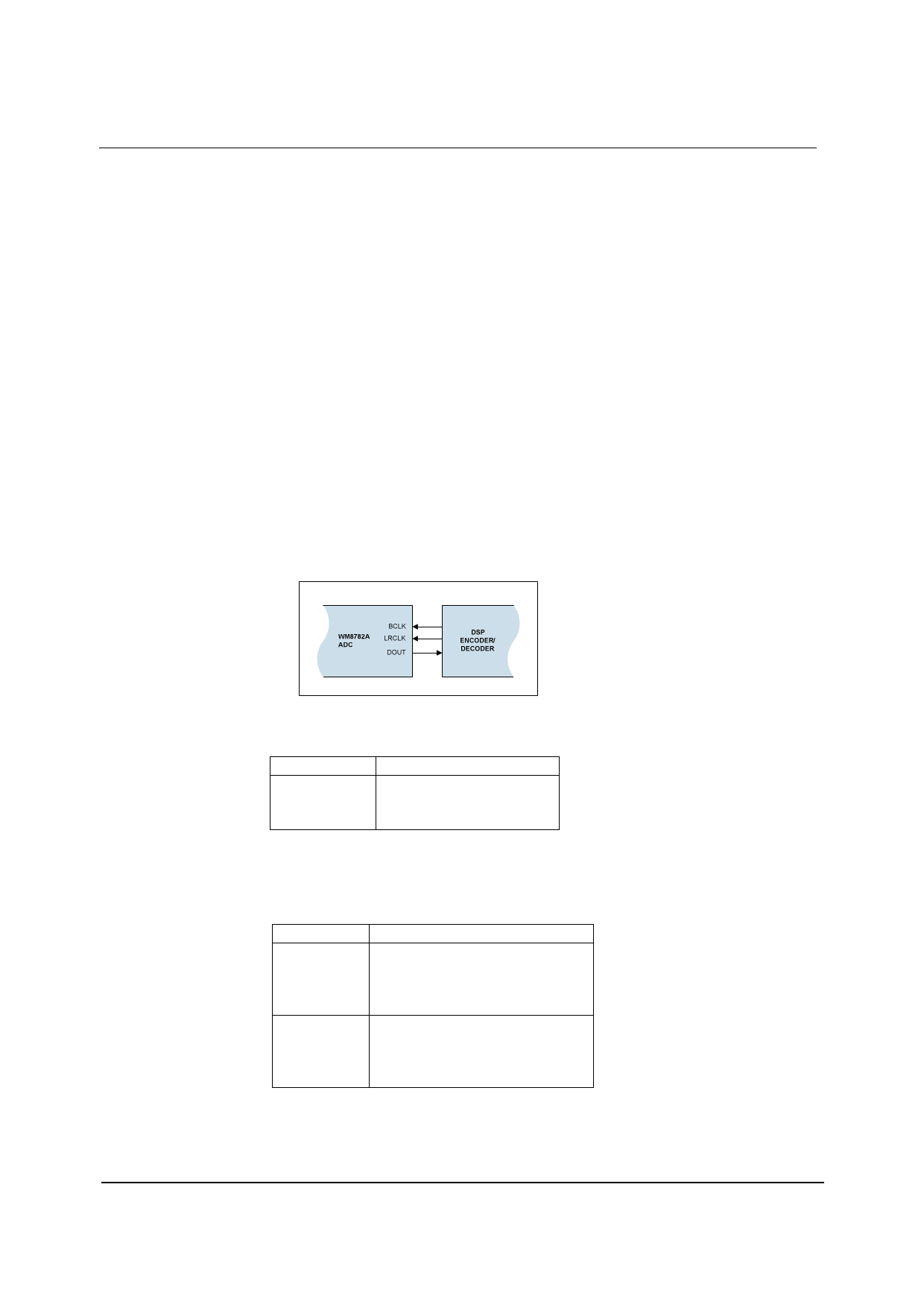

SLAVE MODE OPERATION

The WM8782A can be configured as a slave mode device. In slave mode, the WM8782A responds

with data to clocks it receives over the digital audio interface. The mode is selected by setting the MS

input pin (see Table 3 Slave selection below). Slave mode is illustrated below.

Figure 4 Slave Mode

PIN DESCRIPTION

M/S Slave Selection

0 = Slave Mode

1= Reserved

Table 3 Slave selection

AUDIO INTERFACE CONTROL

The Input Word Length and Audio Format mode can be selected by using IWL and FORMAT pins.

PIN DESCRIPTION

IWL Word Length

0 = 16 bit

1 = 20 bit

Z = 24 bit

FORMAT

Audio Mode Select

0 = RJ

1 = LJ

Z = I2S

Table 4 Audio Data Format Control

w

PD, April 2010, Rev 4.8

11

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet WM8782A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| WM8782 | Stereo ADC | Wolfson Microelectronics |

| WM8782A | Stereo ADC | Wolfson Microelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |