|

|

PDF TCC8801 Data sheet ( Hoja de datos )

| Número de pieza | TCC8801 | |

| Descripción | High Performance and Low-Power Processor | |

| Fabricantes | Telechips | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de TCC8801 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

CHIP

SPECIFICATION

TCC8801

High Performance and Low-Power Processor

For Digital Media Applications

Rev. 1.02

Mar 10, 2011

1 page

TCC8801

TCC8801_CHIP_SPEC

High Performance and Low-Power Processor for Digital Media Applications

Mar 10, 2011

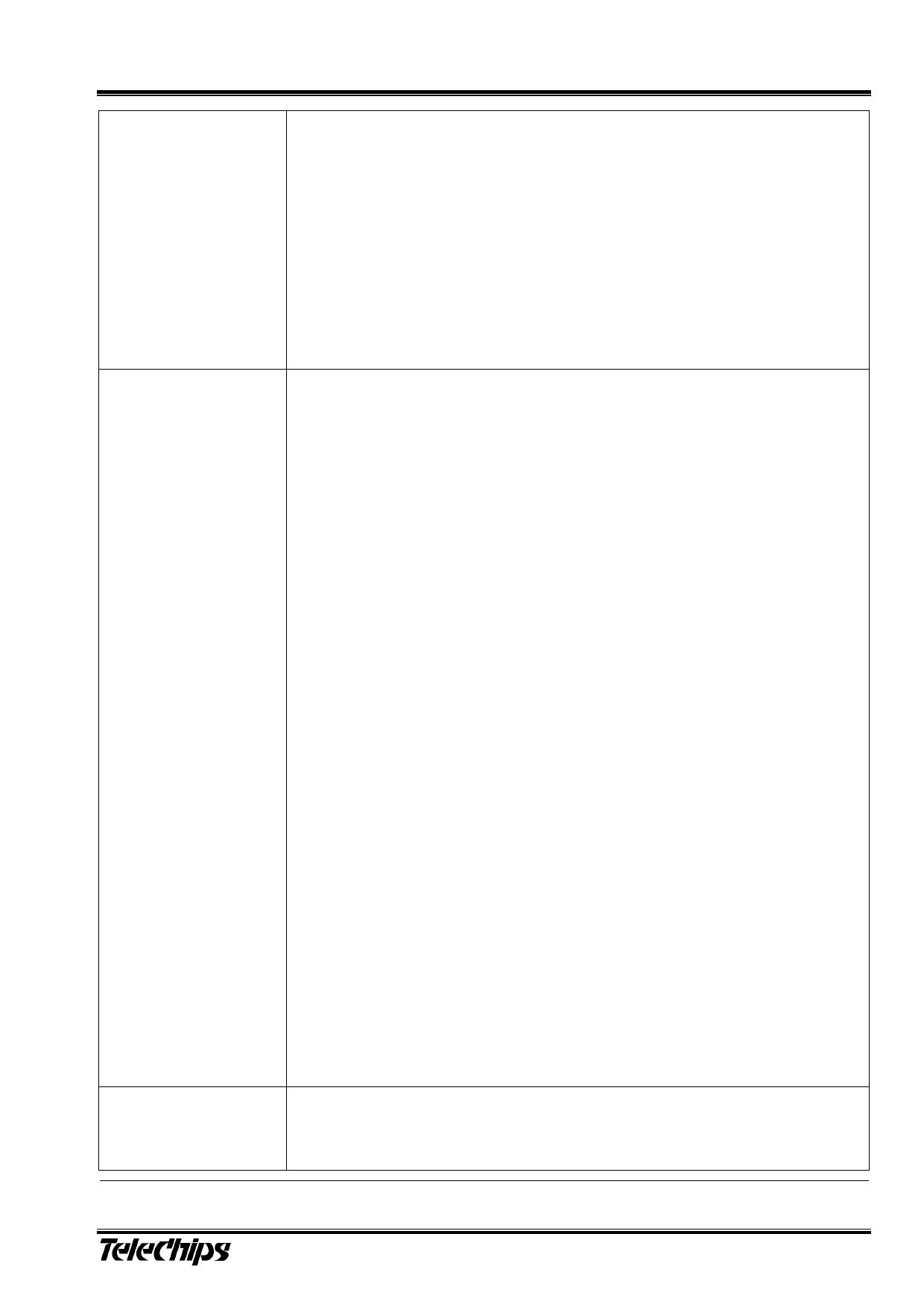

TABLE OF CONTENTS

TABLE OF CONTENTS

Contents

1 Introduction ........................................................................................................................................................................ 1-1

1.1 TCC8801 Features................................................................................................................................................... 1-2

1.2 Applications .............................................................................................................................................................. 1-7

1.3 Block Diagram.......................................................................................................................................................... 1-8

2 Hardware Features............................................................................................................................................................. 2-9

3 PIN Description ................................................................................................................................................................ 3-19

3.1 TCC8801 Pin Description....................................................................................................................................... 3-19

3.2 TCC8801 I/O Type ................................................................................................................................................. 3-26

4 Package Information ........................................................................................................................................................ 4-29

4.1 Dimension .............................................................................................................................................................. 4-29

4.2 Ball Map ................................................................................................................................................................. 4-31

5 Electrical Specification...................................................................................................................................................... 5-35

5.1 Absolute Maximum Ratings.................................................................................................................................... 5-35

5.2 Recommended Operating Conditions .................................................................................................................... 5-35

5.3 Recommended Operating Frequency .................................................................................................................... 5-36

5.4 Electrical Characteristics for Power Supply............................................................................................................ 5-39

5.5 Electrical Characteristics for General I/O ............................................................................................................... 5-39

5.6 Electrical Characteristics for PLL ........................................................................................................................... 5-40

5.7 Electrical Characteristics for Video DAC ................................................................................................................ 5-40

5.8 Electrical Characteristics for ADC(for Touch Screen) ............................................................................................. 5-41

5.9 Electrical Characteristics for HDMI PHY ................................................................................................................ 5-41

5.10 Electrical Characteristics for SATA ....................................................................................................................... 5-41

5.11 Electrical Characteristics for LCD Interface .......................................................................................................... 5-42

5.12 Electrical Characteristics for Camera Interface .................................................................................................... 5-44

5.13 Electrical Characteristics for External Host Interface (EHI) .................................................................................. 5-45

5.14 Electrical Characteristics for SD/MMC Controller................................................................................................. 5-46

5.15 Electrical Characteristics for I2C Controller.......................................................................................................... 5-47

5.16 Electrical Characteristics for SPDI/F Transmitter ................................................................................................. 5-47

5.17 Electrical Characteristics for DAI(I2S) .................................................................................................................. 5-48

5.18 Electrical Characteristics for Nand Flash Controller ............................................................................................. 5-49

5.19 Electrical Characteristics for UART Controller...................................................................................................... 5-52

5.20 Electrical Characteristics for DDR ........................................................................................................................ 5-55

Figures

Figure 1.1 TCC8801 Functional Block Diagram...................................................................................................... 1-8

Figure 2.1 Memory Organization............................................................................................................................. 2-9

Figure 4.1 TCC8801 Package Dimension............................................................................................................. 4-30

Figure 4.2 TCC8801 Ball Map............................................................................................................................... 4-33

Figure 5.1 Timing Diagram for LCD Controller ...................................................................................................... 5-42

Figure 5.2 Timing Diagram Data Output Referenced to PXCLK ........................................................................... 5-42

Figure 5.3 Timing Diagram Data Output Referenced to LCDSI............................................................................. 5-43

Figure 5.4 Timing Diagram for Camera Interface .................................................................................................. 5-44

Figure 5.5 Timing Diagram Data Output Referenced to CCLK.............................................................................. 5-44

Figure 5.6 EHI Timing Diagram............................................................................................................................. 5-45

Figure 5.7 Timing Diagram for SD/MMC Controller............................................................................................... 5-46

Figure 5.8 Timing Diagram for I2C Controller........................................................................................................ 5-47

Figure 5.9 Timing Diagram for SPDI/F Transmitter ............................................................................................... 5-47

Figure 5.10 Timing Diagram for DAI (receiver)...................................................................................................... 5-48

Figure 5.11 Timing Diagram for Command Latch Enable Cycle............................................................................ 5-49

Figure 5.12 Timing Diagram for Single Address Latch Cycle ................................................................................ 5-49

Figure 5.13 Timing Diagram for Linear Address Latch Cycle ................................................................................ 5-49

Figure 5.14 Timing Diagram for Single Data Write Cycle ...................................................................................... 5-49

Figure 5.15 Timing Diagram for Linear Data Write Cycle ...................................................................................... 5-50

Figure 5.16 Timing Diagram for Single Data Read Cycle...................................................................................... 5-50

Figure 5.17 Timing Diagram for Linear Data Read Cycle...................................................................................... 5-50

Figure 5.18 Timing Diagram for TXD..................................................................................................................... 5-52

Figure 5.19 Timing Diagram for RXD .................................................................................................................... 5-52

Figure 5.20 Timing Diagram for TX Operation with H/W Flow Control .................................................................. 5-53

Figure 5.21 Timing Diagram for nCTS Timing Diagram ........................................................................................ 5-53

Figure 5.22 Timing Diagram for RX Operation with H/W Flow Control.................................................................. 5-54

Figure 5.23 Timing Diagram for nRTS Timing Diagram......................................................................................... 5-54

Figure 5.24 Write Cycle Timing ............................................................................................................................. 5-55

Figure 5.25 Read Cycle Timing............................................................................................................................. 5-55

5

5 Page

TCC8801

TCC8801_CHIP_SPEC

High Performance and Low-Power Processor for Digital Media Applications

• RV

- Real Video 10 ( Backward Compatible for RV 8/9)

- Max. bitrate : up to 30Mbps

• AVS

- Jizhun Profile @ L6.2

- Max. bitrate : up to 40Mbps

• MJPEG/JPEG

- Up to 32M pixel/s

- Max Image Size : 8192 x 8192

▪ Compressor3 (Encoder) – up to 24fps ~ 30 fps @FHD(1920x1080)

• H.263

: up to 30fps @ FHD(1920x1080p)

• MPEG4-ASP : up to 30fps @ FHD(1920x1080p)

• H.264

: up to 24fps ~ 30 fps @ FHD(1920x1080p)

• MJPEG/JPEG : up to 32M pixel/s (Max 4096x4096)

Mar 10, 2011

INTRODUCTION

GRAPHIC ENGINE

▪ 2D/3D Graphic

• High Geometry and Pixel Processing

• Up to 20M polygon4

• Full OpenVG v1.1 Support

- Lines, Squares, Triangles, Points

- Vector Graphics

- ROP 3/4

- Arbitrary Rotation / Scaling

- Alpha Blending

- Multitexture BItBLT

• Full OpenGL ES v2.0, v1.x Support

- 4X /16X FSAA

- Flat/Gouraud Shading

- Perspective Correct Texturing

- Point Sampling/Bilinear/Trilinear Filtering

- Mipmapping

- Multi Texturing

- Dot3 Bump Mapping

- Alpha Blending

- Stencil Buffering (4-bit)

- JSR 184

- Point Sprites

- 2 bit per pixel Texture Compressing (FLXTC)

- 4 bit per pixel Texture Compressing (ETC)

▪ Overlay Mixer

- 8bpp (RGB332)

- RGB (444, 454, 555, 565, 666, 888)

- Alpha-RGB (444, 454, 555, 666, 888)

- Sequential YUV (444, 422)

- Separated YUV (444, 440, 422, 420, 411, 410)

- Interleaved YUV (422, 420)

- BitBLT (16 Raster Operations)

- 3 Channel Source Mirror/Flip/90°, 180°, 270° Rotate

- 1 Channel Destination Mirror/Flip/90°, 180°, 270° Rotate

- 3 Channel Arithmetic Operation

- 3 Channel YCbCr-to-RGB Color Space Converting

- Overlay and Alphablending (2 overlay, 256-level alphablending)

- Color LUT

- Dithering

IMAGE ENHANCEMENT

• Histogram Measurement

- Analyze the Luminance Components

- Multi-frames Average Mode

- User-defined Pixel Segments Support

3 The performance of the video encoding can be limited by the overall system bus traffic

4 The performance of the polygon processing can be limited by the overall system bus traffic

1-3

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet TCC8801.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TCC8801 | High Performance and Low-Power Processor | Telechips |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |